Trustworthy System-on-Chip Design using Secure On-Chip Communication Architecture |

Overview

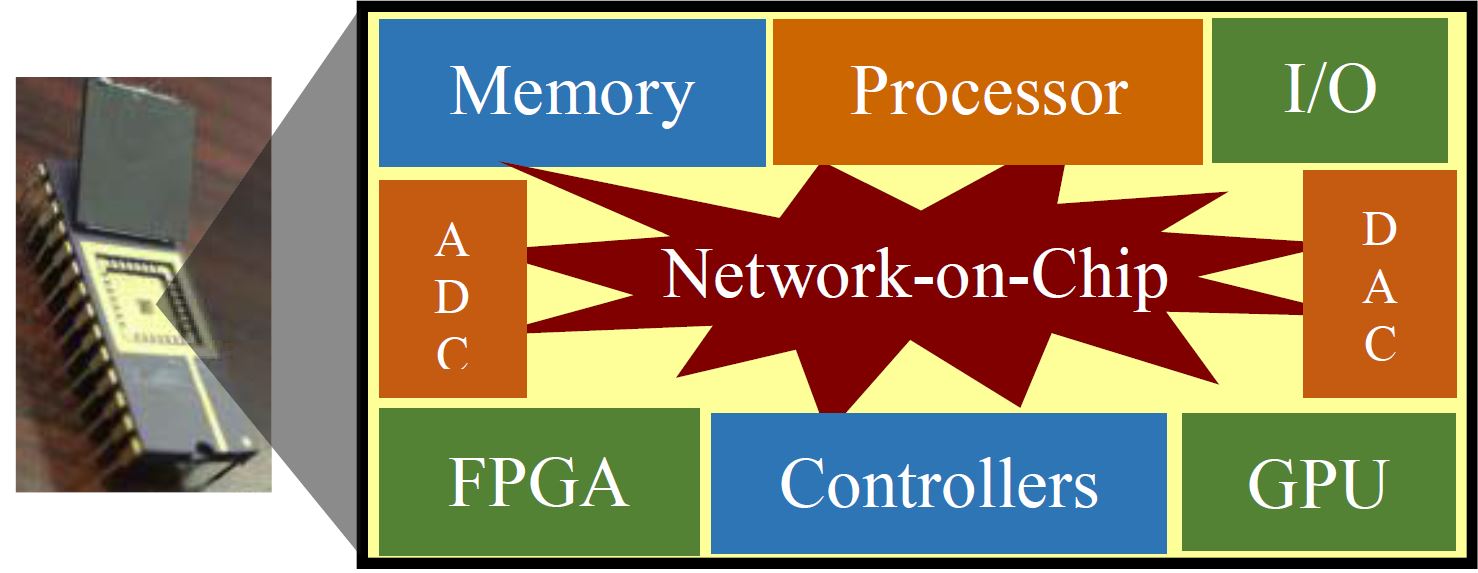

System-on-Chip (SoC) is the brain behind computing and communication in a wide variety of systems,

starting from simple handheld devices to complex supercomputers. Cars are full of them, as are airplanes,

satellites, and advanced military and medical devices. As applications grow increasingly complex, so do

the complexities of the SoCs. For example, a typical automotive SoC may include 100-200 diverse

Intellectual Property (IP) blocks from multiple third-party vendors. Network-on-Chip (NoC) is a widely

used solution for on-chip communication between IPs in complex SoCs. A study by Gartner Research

reveals that the demand for NoC IPs is growing rapidly (44.8% in one year). Unlike microcontroller

based designs in the past, even resource constrained IoT (Internet-of-Things) devices nowadays

incorporate one or more NoC-based SoCs. SoCs are designed today using hardware IPs to reduce cost

while meeting aggressive time-to-market constraints. Growing reliance on these pre-verified hardware

IPs, often gathered from untrusted third-party vendors, severely affects the security and trustworthiness of

SoC computing platforms. Based on Common Vulnerability Exposure (CVE-MITRE) estimates, if

hardware-level vulnerabilities are removed, the overall system vulnerability will reduce by 43%. Clearly,

there is a critical need to design secure and trustworthy SoCs by ensuring security of computation,

communication as well as storage.

In spite of increasing importance of trusted

communication in overall system security, there is limited research effort in NoC security. The goal of this proposal is to

develop a lightweight and secure on-chip communication architecture to enable trusted

communication between heterogeneous third-party IPs in NoC-based SoCs.

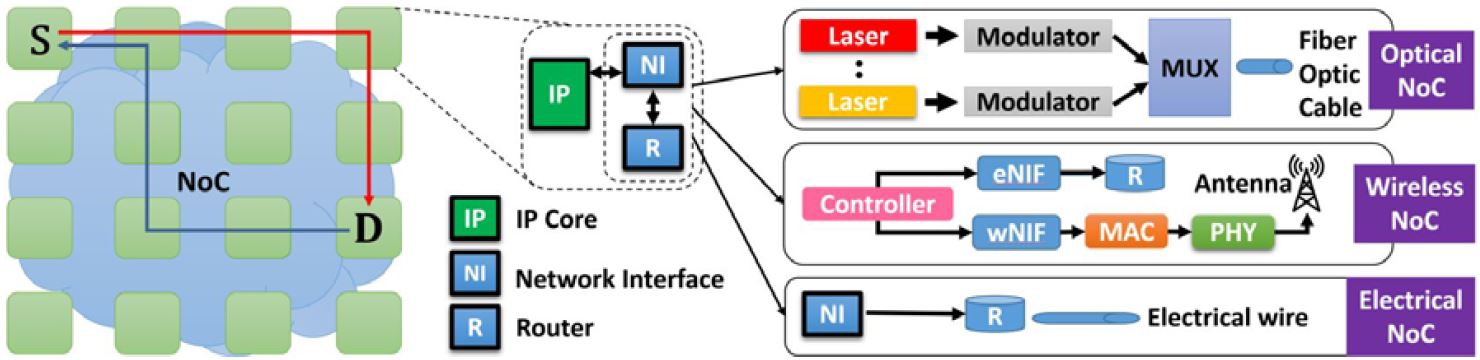

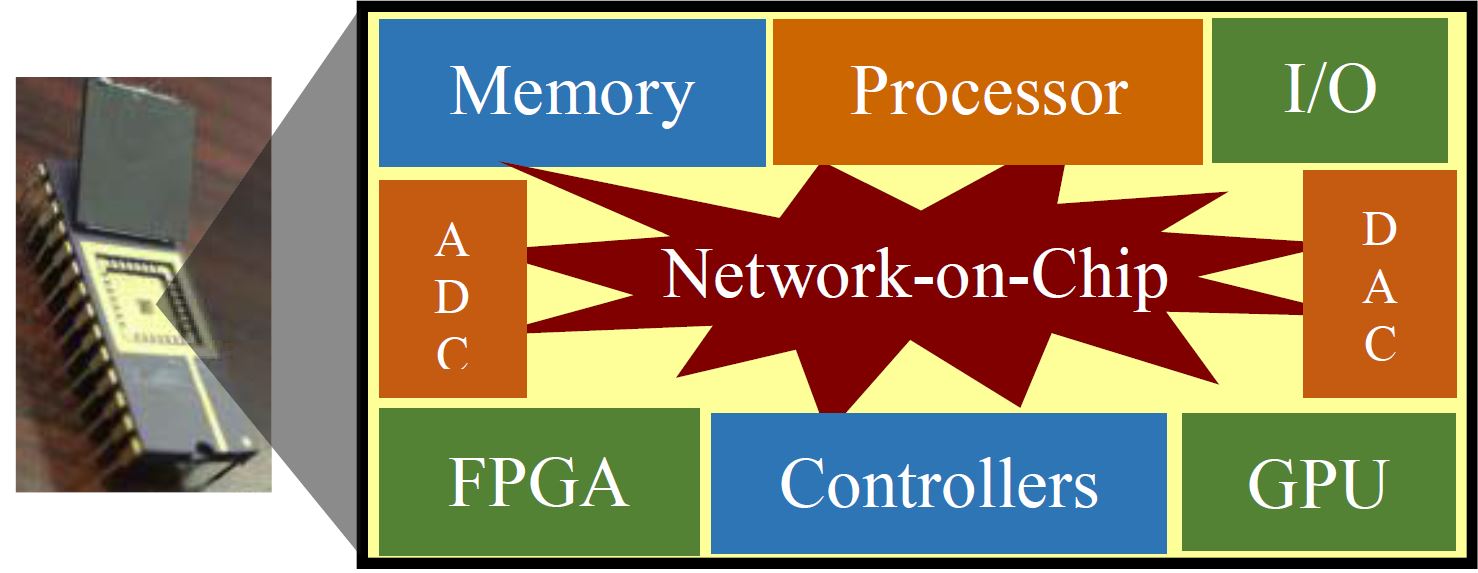

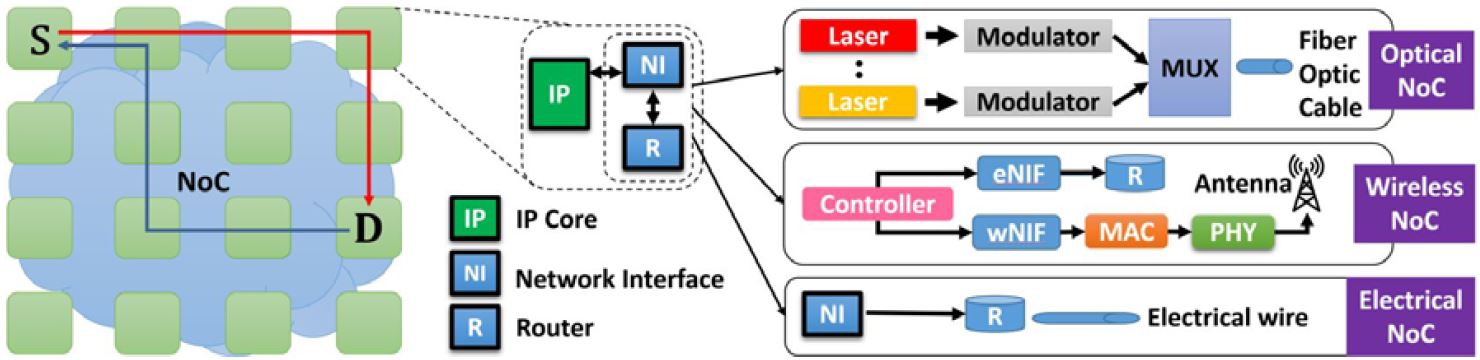

The above figure shows an example SoC with NoC based communication fabric to interact with a wide variety of third party IP cores. The proposed research will make two fundamental contributions that represent a paradigm shift in

securing on-chip communication architectures. (1) Unlike existing approaches that are applicable for a

specific communication scenario, our proposed research will be applicable across on-chip communication

technologies (e.g., electrical, optical, and wireless) supporting a wide variety of on-chip network

topologies (e.g., point-to-point, bus, crossbar, ring, mesh, etc.). (2) Our proposed research will provide a

comprehensive solution by addressing the fundamental on-chip communication security challenges while

satisfying a wide variety of communication requirements such as securing packets, ensuring route

privacy, meeting energy budget and real-time constraints, finding trusted routes in the presence of

malicious IPs, and providing real-time attack detection and mitigation techniques. Specifically, the

proposed research will develop automated tools and techniques to address five fundamental challenges in

designing a secure on-chip communication architecture: (i) lightweight NoC security architecture that

secures the content of packets without compromising energy efficiency and real-time constraints, (ii)

anonymous routing to maintain route privacy, (iii) trust-aware routing to enable trusted communication in

the presence of potentially malicious IPs, (iv) real-time detection and localization of denial-of-service and

buffer overflow attacks, and (v) validation and evaluation of NoC security architectures. The following figure shows NoC implementations using optical, wireless or electrical communication technologies.

Members

Downloads

Stay tuned ...

Publications

Books:

PhD Dissertations:

Journal Articles:

| J7 |

Meenu Dey, Moumita Patra and Prabhat Mishra, Efficient Detection and Localization of DoS Attacks in Heterogeneous Vehicular Networks, IEEE Transactions on Vehicular Technology (TVT), 2022. |

| J6 |

Chamika Sudusinghe, Subodha Charles, Sapumal Ahangama and Prabhat Mishra, Eavesdropping Attack Detection using Machine Learning in Network-on-Chip Architectures, IEEE Design & Test (D&T), 2022. |

| J5 |

Subodha Charles, Vincent Bindschaedler and Prabhat Mishra, Digital Watermarking for Detecting Malicious Intellectual Property Cores in NoC Architectures, IEEE Transactions on Very Large Scale Integration (VLSI) Systems (TVLSI), 2022. |

| J4 |

Subodha Charles and Prabhat Mishra, A Survey of Network-on-Chip Security Attacks and Countermeasures, ACM Computing Surveys (CSUR), 54(5), article 101, pages 1-36, 2021. |

| J3 |

Subodha Charles and Prabhat Mishra, Reconfigurable Network-on-Chip Security Architecture, ACM Transactions on Design Automation of Electronic Systems (TODAES), 2020. |

| J2 |

Subodha Charles, Yangdi Lyu and Prabhat Mishra, Real-time Detection and Localization of Distributed DoS Attacks in NoC based SoCs, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2020. |

| J1 |

Subodha Charles, Alif Ahmed, Umit Ogras and Prabhat Mishra, Efficient Cache Reconfiguration using Machine Learning in NoC-based Many-Core CMPs, ACM Transactions on Design Automation of Electronic Systems (TODAES), 24(6), Article 60, September 2019. |

Referred Conference Papers:

| C11 |

Chamika Sudusinghe, Subodha Charles, Sapumal Ahangama and Prabhat Mishra, Eavesdropping Attack Detection using Machine Learning in Network-on-Chip Architectures, IEEE/ACM International Symposium on Networks-on-Chip (NOCS), October 7-14, 2022. |

| C10 |

Hansika Weerasena, Subodha Charles and Prabhat Mishra, Lightweight Encryption using Chaffing and Winnowing with All-or-Nothing Transform for Network-on-Chip Architectures, IEEE International Symposium on Hardware Oriented Security and Trust (HOST), Washington DC, December 12-15, 2021. |

| C9 |

Chamika Sudusinghe, Subodha Charles and Prabhat Mishra, Denial-of-Service Attack Detection using Machine Learning in Network-on-Chip Architectures, IEEE/ACM International Symposium on Networks-on-Chip (NOCS), October 8-15, 2021. |

| C8 |

Meenu Dey, Moumita Patra and Prabhat Mishra, Real-Time Detection and Localization of Denial-of-Service Attacks in Heterogeneous Vehicular Networks, Design Automation and Test in Europe (DATE), Grenoble, France, February 1-5, 2021. |

| C7 |

Zhixin Pan, Jennifer Sheldon, Chamika Sudusinghe, Subodha Charles and Prabhat Mishra, Hardware-Assisted Malware Detection using Machine Learning, Special Session on Hardware-based Malware Detectors in Design Automation and Test in Europe (DATE), Grenoble, France, February 1-5, 2021. |

| C6 |

Manju R, Abhijit Das, John Jose and Prabhat Mishra, SECTAR: Secure NoC using Trojan Aware Routing, IEEE/ACM International Symposium on Networks-on-Chip (NOCS), September 24-25, 2020. |

| C5 |

Subodha Charles and Prabhat Mishra, Lightweight and Trust-aware Routing in NoC Based SoCs, IEEE Annual Symposium on VLSI (ISVLSI), Limassol, Cyprus, July 6-8, 2020. |

| C4 |

Subodha Charles and Prabhat Mishra, Securing Network-on-Chip Using Incremental Cryptography, IEEE Annual Symposium on VLSI (ISVLSI), Limassol, Cyprus, July 6-8, 2020. |

| C3 |

Subodha Charles, Megan Logan and Prabhat Mishra, Lightweight Anonymous Routing in NoC based SoCs, Design Automation and Test in Europe (DATE), Grenoble, France, March 9 - 13, 2020. |

| C2 |

Subodha Charles, Yangdi Lyu, Prabhat Mishra, Real-time Detection and Localization of DoS

Attacks in NoC based SoCs, Design Automation and Test in Europe (DATE), Florence, Italy, March 25 - 29, 2019. |

| C1 |

Subodha Charles, Yangdi Lyu, Prabhat Mishra, Real-time Detection and Localization of DoS

Attacks in NoC based SoCs, Design Automation and Test in Europe (DATE), Florence, Italy, March 25 - 29, 2019. |

Patents and Copyrights:

| P7 |

Prabhat Mishra, Hansika Weerasena and Subodha Charles, Securing On-Chip Communication using Chaffing and Winnowing with All-or-Nothing Transform, U.S. Provisional Patent Application Serial No. 63/275,552, filed November 4, 2021. |

| P6 |

Prabhat Mishra, Subodha Charles and Vincent Bindschaedler, Securing On-Chip Communication using Digital Watermarking, U.S. Non-Provisional Patent Application Serial No. 17/525,176, filed November 12, 2021. |

| P5 |

Prabhat Mishra and Subodha Charles, Reconfigurable Network-on-Chip Security Architecture, U.S. Provisional Patent Application Serial No. 62/937,858, filed November 20, 2019. |

| P4 |

Subodha Charles and Prabhat Mishra, Lightweight and Trust-aware Routing in NoC based SoC Architectures, U.S. Utility Patent Application Serial No. 16/934,612, filed July 21, 2020. |

| P3 |

Prabhat Mishra, Subodha Charles and Yangdi Lyu, Securing System-on-Chip using Incremental Cryptography, U.S. Non-Provisional Patent Application Serial No. 16/915,021, filed June 29, 2020. |

| P2 |

Subodha Charles and Prabhat Mishra, Lightweight Encryption and Anonymous Routing in NoC based SoCs, U.S. Utility Patent Application Serial No. 16/937,882 filed July 24, 2020. |

| P1 |

Prabhat Mishra, Subodha Charles and Yangdi Lyu, Real-Time Detection and Localization of DoS Attacks in NoC based SoC Architectures, U.S. Utility Patent Application Serial No. 16/913,850, filed June 26, 2020. |

Research Sponsors

|

This project is funded by the National Science Foundation (NSF) grant 1936040. The views expressed on the site are those of the members of

this project and do not necessarily represent those of the National Science Foundation. |