### SCALABLE SIGNAL SELECTION FOR POST-SILICON DEBUG

## By KAMRAN RAHMANI

A DISSERTATION PRESENTED TO THE GRADUATE SCHOOL

OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT

OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

UNIVERSITY OF FLORIDA

2017

#### **ACKNOWLEDGMENTS**

First of all, I would like to thank my adviser Prof. Prabhat Mishra for all his help and support throughout this journey. It was him who led me to explore unknowns and to grow and push the boundaries. He taught me how to explore new directions and how to present my findings. He is the person who made this dissertation come true. I would also like to thank my Ph.D. committee members: Prof. Sartaj Sahni, Prof. Sanjay Ranka, Prof. Shigang Chen, and Prof. Nima Maghari for their valuable input and suggestions.

I would like to take this opportunity to thank those who helped me during different stages of my research. I would like to thank Dr. Sandip Ray from NXP (Qualcomm) who helped me understand the industry challenges in post-silicon debug. I sincerely thank Prof. Swarup Bhunia for helping me understand various aspect of memory-based computing. I am also thankful to my labmates Hadi Hajimiri, Sudhi Proch, Kanad Basu, Weixun Wang, and Xiaoke Qin for their help and support.

Last but not least, I would also like to extend my gratitude towards my family and their unconditional support and help.

.

### TABLE OF CONTENTS

|                                                                                                                                                                                                                                                                                                                                         |              | page                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------|

| ACKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                         |              | 4                                |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                          |              | 7                                |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                         |              | 8                                |

| ABSTRACT                                                                                                                                                                                                                                                                                                                                |              | 10                               |

| CHAPTER                                                                                                                                                                                                                                                                                                                                 |              |                                  |

| 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                          |              | 11                               |

| 1.1Signal Restoration in Post Silicon Validation1.2Challenges1.3Research Contributions1.4Dissertation Organization                                                                                                                                                                                                                      |              | 14<br>16                         |

| 2 BACKGROUND AND RELATED APPROACHES                                                                                                                                                                                                                                                                                                     |              | 18                               |

| 2.1       Trace Signal Selection         2.2       Dynamic Signal Selection         2.3       Supervised Learning and Prediction         2.4       Trace Data Compression         2.5       Observability-Aware Test Generation         2.6       Post-silicon Debug Techniques         2.7       Combination of Trace and Scan Signals |              | 20<br>21<br>22<br>22<br>23       |

| 3 TRACE SIGNAL SELECTION USING AUGMENTATION AND ILP                                                                                                                                                                                                                                                                                     | TECHNIQUES . | 26                               |

| 3.1 Augmentation-based Selection                                                                                                                                                                                                                                                                                                        |              | 29<br>31<br>33                   |

| 3.2       Experiments         3.2.1       Experimental Setup         3.2.2       Results         3.2.2.1       Restoration quality         3.2.2.2       Selection time         3.3       Summary                                                                                                                                       |              | 34<br>34<br>35<br>35<br>36<br>38 |

| 4 EFFICIENT COMBINATION OF TRACE AND SCAN SIGNALS                                                                                                                                                                                                                                                                                       |              | 39                               |

| 4.1 Fine-grained Combinations                                                                                                                                                                                                                                                                                                           |              | 43<br>43<br>44<br>49             |

|     | 4.2  | Experiments                                        | 53 |

|-----|------|----------------------------------------------------|----|

|     |      |                                                    | 53 |

|     |      |                                                    | 54 |

|     |      |                                                    | 56 |

|     |      |                                                    | 56 |

|     | 4.3  | Summary                                            | 62 |

| 5   | SCA  | ABLE TRACE SIGNAL SELECTION USING MACHINE LEARNING | 63 |

|     | 5.1  | Learning-based Signal Selection                    | 63 |

|     |      |                                                    | 64 |

|     |      |                                                    | 65 |

|     |      |                                                    | 68 |

|     |      |                                                    | 71 |

|     |      |                                                    | 72 |

|     |      | 5.1.3.3 Final model selection                      | 73 |

|     |      | 5.1.3.4 Elimination-based signal selection         | 75 |

|     |      | 5.1.3.5 Augmentation-based signal selection        | 76 |

|     |      |                                                    | 77 |

|     | 5.2  |                                                    | 78 |

|     |      |                                                    | 79 |

|     |      |                                                    | 81 |

|     |      |                                                    | 82 |

|     |      |                                                    | 82 |

|     | 5.3  | ·                                                  | 83 |

|     |      |                                                    | 85 |

|     |      | · · · · · · · · · · · · · · · · · · ·              | 85 |

|     |      |                                                    | 85 |

|     |      | · · · · · · · · · · · · · · · · · · ·              | 86 |

|     |      |                                                    | 88 |

|     |      | · · · · · · · · · · · · · · · · · · ·              | 90 |

|     |      | · · · · · · · · · · · · · · · · · · ·              | 90 |

|     |      |                                                    | 90 |

|     |      | ·                                                  | 90 |

|     |      | •                                                  | 92 |

|     | 5.4  | Summary                                            | 93 |

| 6   | CON  | CLUSIONS AND FUTURE WORK                           | 95 |

|     | 6.1  | Conclusions                                        | 95 |

|     | 6.2  | Future Research Directions                         | 96 |

| APP | ENDI | K: LIST OF PUBLICATIONS                            | 98 |

| REF | EREN | CES                                                | 99 |

| BIO | GRAP | HICAL SKETCH                                       | 05 |

## LIST OF TABLES

| Table |                                                                                                  | page |

|-------|--------------------------------------------------------------------------------------------------|------|

| 1-1   | Illustration of restored signals for the simple circuit shown in Figure 1-4                      | 15   |

| 3-1   | Illustration of restored signals for the simple circuit shown in Figure 1-4                      | 26   |

| 3-2   | Restored signals for circuits in Figure 1-4                                                      | 27   |

| 3-3   | Restored signals from Chatterjee et al. [7] for the circuit in Figure 3-1                        | 28   |

| 3-4   | Restored signals using our method for the circuit in Figure 3-1                                  | 28   |

| 3-5   | Restoration ratios using our approach compared with existing selection approaches .              | 36   |

| 4-1   | Restored signals for the circuit shown in Figure 4-1                                             | 41   |

| 4-2   | Trace buffer slots and shadow flip-flops values in our proposed debug architecture in Figure 4-2 | 41   |

| 4-3   | Restored signals using our proposed debug architecture in Figure 4-2                             | 42   |

| 4-4   | Different restoration power values of our algorithm in example circuit of Figure 4-1 .           | 49   |

| 4-5   | Restoration impact values of our flexible selection algorithm in example circuit of Figure 4-6   | 52   |

| 4-6   | Different parameters used in CSS                                                                 | 54   |

| 4-7   | Restoration ratios of different trace only approaches compared with our proposed architecture    | 55   |

| 4-8   | Restoration ratios using our approach compared with Basu et al. [3]                              | 56   |

| 4-9   | Runtime comparison of different approaches                                                       | 57   |

| 4-10  | Configurations for fine-grained architectures                                                    | 58   |

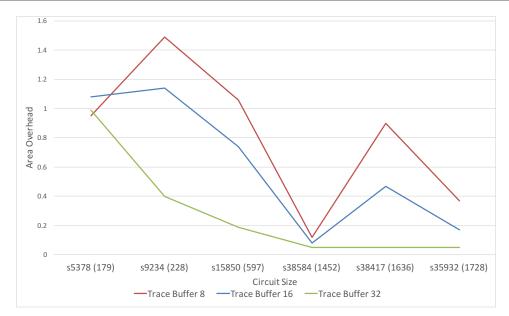

| 4-11  | Area overhead of fine-grained signal selection compared to trace-only approach                   | 60   |

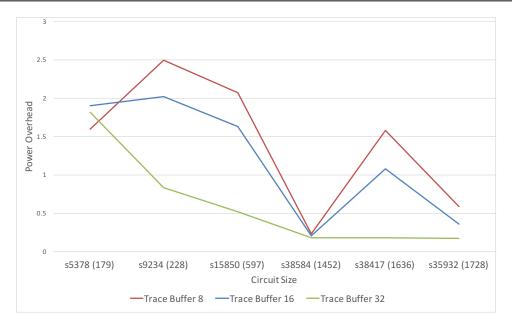

| 4-12  | Power overhead of fine-grained signal selection compared to trace-only approach                  | 61   |

| 5-1   | Time complexity of our approach and existing signal selection techniques                         | 79   |

| 5-2   | Restoration ratios using our approach compared with existing selection approaches .              | 88   |

| 5-3   | Runtime comparison of our approach compared with existing selection approaches $\ \ .$           | 89   |

| 5-4   | Restoration ratios using our approach compared with existing selection approaches .              | 92   |

| 5-5   | Runtime comparison of our approach compared with existing selection approaches .                 | 94   |

### LIST OF FIGURES

| Figu | <u>re</u>                                                                                                                                          | page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1-1  | Different phases of validation and testing in IC design flow                                                                                       | 11   |

| 1-2  | An overview of post-silicon validation flow                                                                                                        | 13   |

| 1-3  | Basic restoration rules for common logic gates                                                                                                     | 14   |

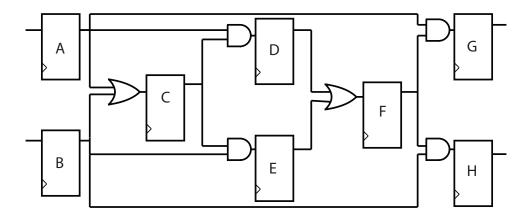

| 1-4  | A simple circuit to illustrate restorability                                                                                                       | 14   |

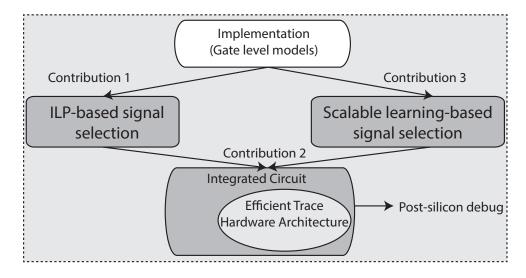

| 1-5  | Overview of research contributions                                                                                                                 | 16   |

| 2-1  | Simulation-based trace signal selection flow                                                                                                       | 20   |

| 2-2  | Two different type of supervised learning                                                                                                          | 21   |

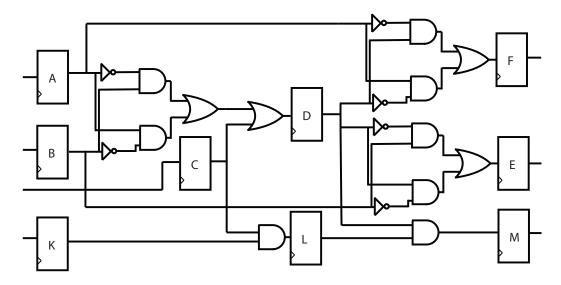

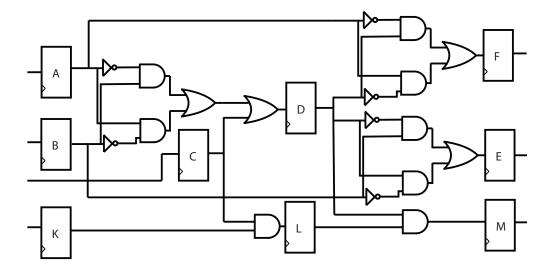

| 3-1  | Example circuit to compare our approach with Chatterjee et al. [7]                                                                                 | 27   |

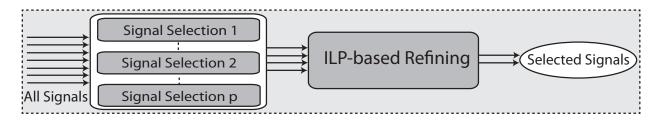

| 3-2  | Proposed signal selection process                                                                                                                  | 29   |

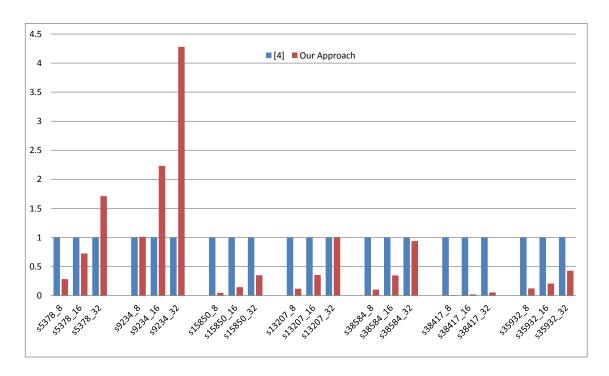

| 3-3  | Selection times of our approaches compared and normalized to Chatterjee et al. [7]                                                                 | 37   |

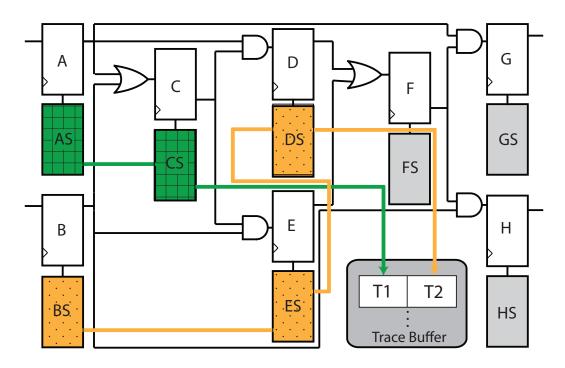

| 4-1  | Simple circuit to illustrate restorability used in Basu et al. [3]                                                                                 | 40   |

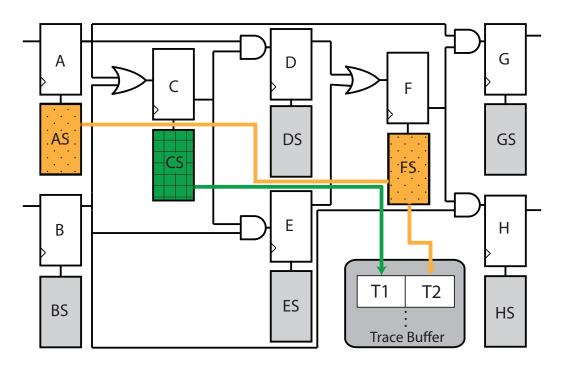

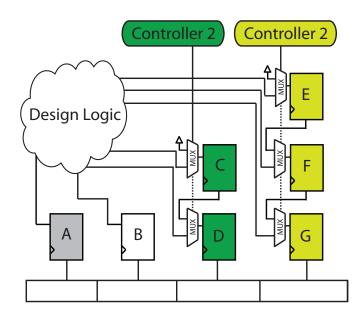

| 4-2  | Proposed debug architecture for example circuit in Figure 4-1                                                                                      | 42   |

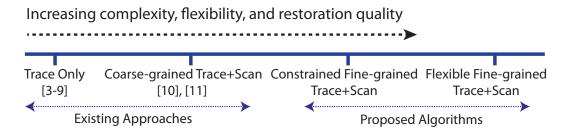

| 4-3  | Spectrum of existing and proposed debug architectures                                                                                              | 43   |

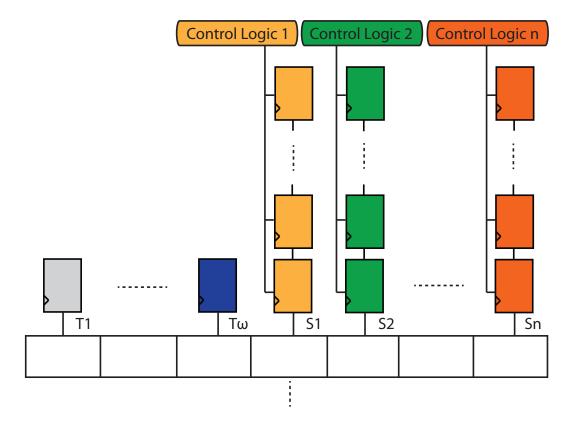

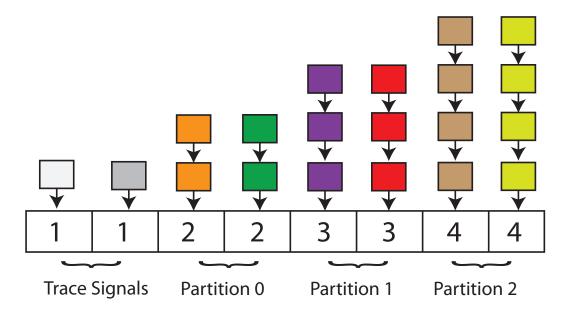

| 4-4  | Proposed debug architecture                                                                                                                        | 45   |

| 4-5  | An example of trace buffer partitioning                                                                                                            | 46   |

| 4-6  | Sample circuit to illustrate our flexible selection algorithm                                                                                      | 51   |

| 4-7  | Sample scan-trace configuration                                                                                                                    | 58   |

| 4-8  | Area overhead of our approach for different circuit and trace sizes, benchmarks are ordered based on the number of flip-flops (shown in brackets)  | 60   |

| 4-9  | Power overhead of our approach for different circuit and trace sizes, benchmarks are ordered based on the number of flip-flops (shown in brackets) | 61   |

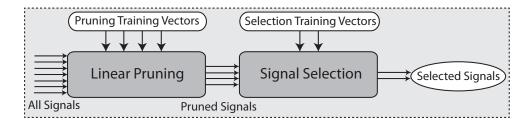

| 5-1  | Overview of our approach and its relation to existing simulation based approaches .                                                                | 65   |

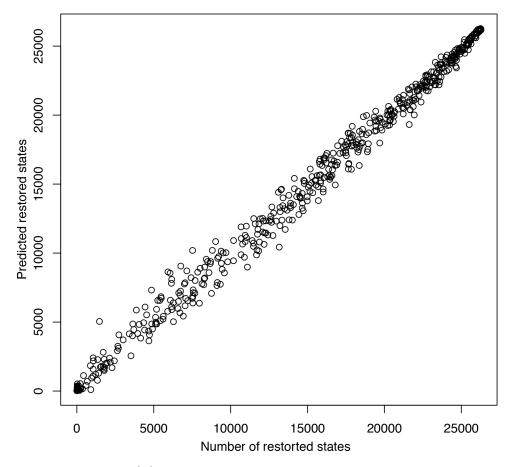

| 5-2  | Real values of $r_m(v)$ versus predicted values for different random vectors in s38417 benchmark                                                   | 67   |

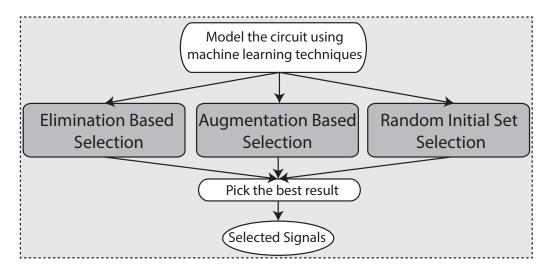

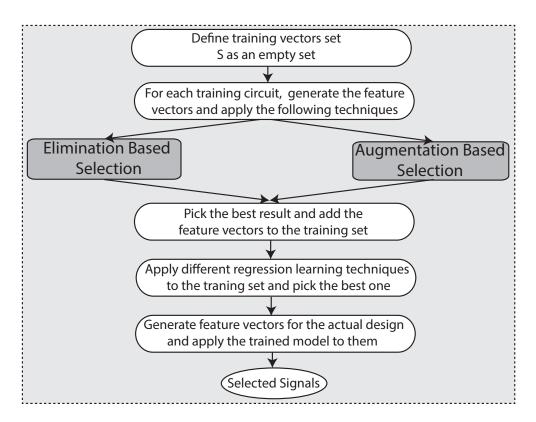

| 5-3  | Proposed signal selection process                                                                                                                  | 68   |

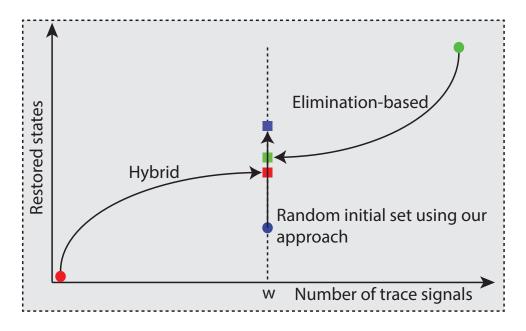

| 5-4  | Different signal selection techniques for exploring the search space                                                                               | 69   |

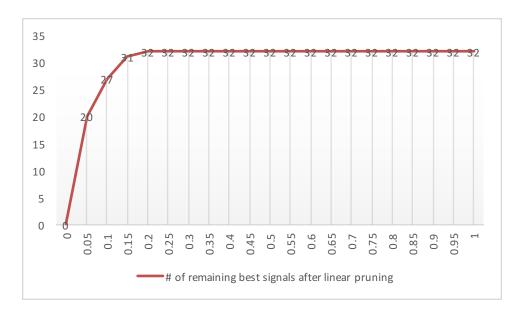

| 5-5  | Number of profitable signals remaining after linear pruning                                | 73 |

|------|--------------------------------------------------------------------------------------------|----|

| 5-6  | Overview of our proposed approach and its relation to existing simulation based approaches | 80 |

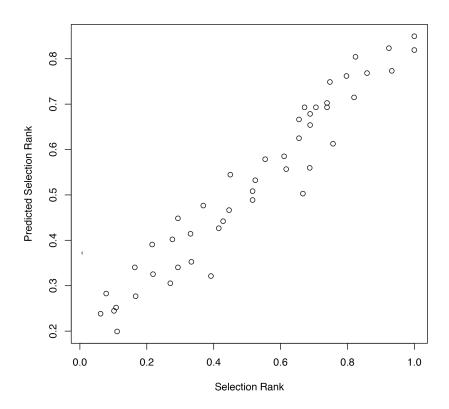

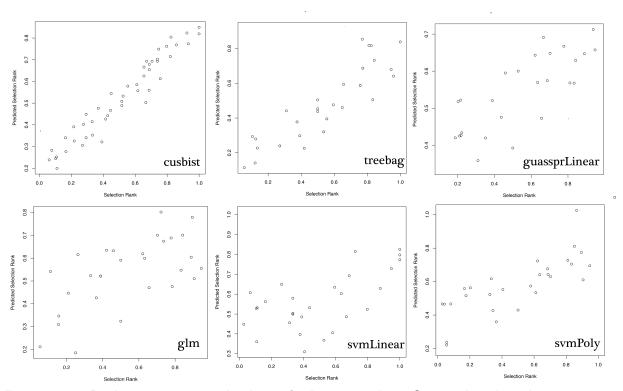

| 5-7  | Actual versus predicted values of selection ranks in s38584 benchmark                      | 84 |

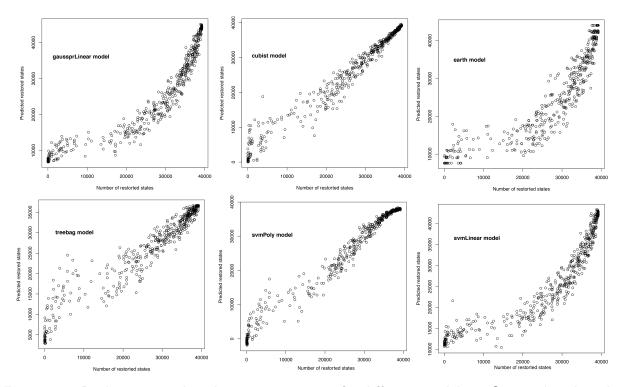

| 5-8  | Real versus predicted restoration states for different models in $\it S38584$ benchmark .  | 86 |

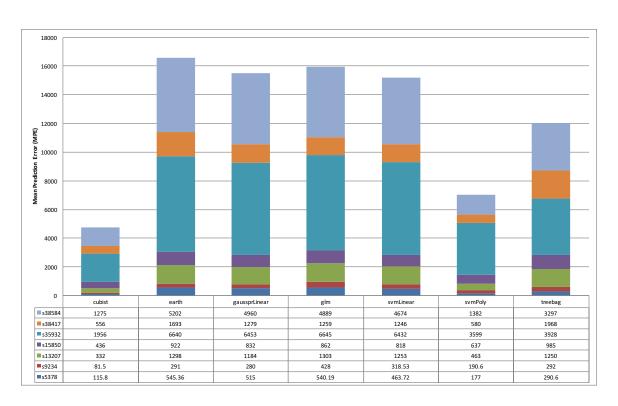

| 5-9  | Mean prediction errors (MPE) of different models on the set of our benchmarks $$ . $$      | 87 |

| 5-10 | Real versus estimated values of selection rank on S38584 benchmark                         | 91 |

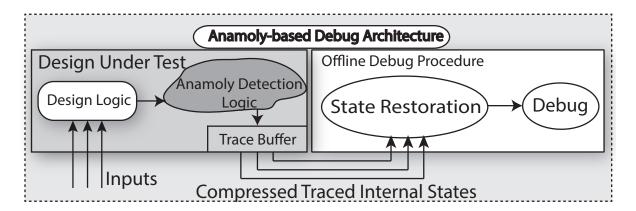

| 6-1  | Overview of our proposed anomaly-based debug architecture                                  | 97 |

Abstract of Dissertation Presented to the Graduate School of the University of Florida in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

#### SCALABLE SIGNAL SELECTION FOR POST-SILICON DEBUG

By

#### Kamran Rahmani

May 2017

Chair: Prabhat Mishra

Major: Computer Engineering

The goal of post-silicon validation is to ensure that the fabricated, pre-production silicon functions correctly while running actual applications under on-field operating conditions. Post-silicon validation is a complex activity performed under aggressive schedule, accounting for more than 50% of the overall validation cost of a modern integrated circuit [1, 2]. A fundamental challenge in post-silicon validation is limited observability and controllability. Design overhead considerations impose restrictions that only a few hundreds among the millions of internal signals can be traced during a silicon execution. Furthermore, in order for a signal to be observed, the design must be instrumented a priori with appropriate hardware that routes the signal to an observation point. It is therefore crucial to develop techniques to identify trace signals that maximize design visibility under post-silicon observability restrictions. This dissertation proposes novel techniques to enhance the observability during post-silicon debug. My research has three major contributions. First, it proposes efficient signal selection techniques to enhance the observability of the circuit. Next, to improve the observability further, a new fine-grained scan and trace combination architecture has been proposed. Finally, the application of machine learning techniques has been extensively explored to improve the scalability of selection techniques. Extensive experimental results exhibit significant improvement in both overall signal observability and signal selection time.

10

## CHAPTER 1 INTRODUCTION

Design complexity is rapidly increasing with drastic growth of number of transistors in each technology cycle. This has caused a significant increase in validation complexity. In spite of extensive effort on design validation using simulation and formal methods, it is not always possible to detect all the functional and electrical errors and bugs in pre-silicon validation. Post-silicon validation is used to capture the design flaws and escaped errors.

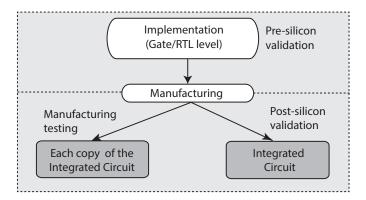

Figure 1-1 illustrates the different phases of validation and testing in a typical chip design flow. Pre-silicon validation includes validation of different functional and timing requirements of the specification and implementation. Manufacturing testing is used to detect the physical defects of each IC. In addition, post-silicon validation is used to detect design errors that have escaped pre-silicon validation phase. It should be noted that most of the electrical bugs such as crosstalk and transient faults are captured during post-silicon validation as it is difficult to model and fix those in pre-silicon validation. Post-silicon validation is a complex activity performed under aggressive schedules, representing more than 50% of the overall validation cost [1]. A fundamental challenge in post-silicon validation is limited observability and controllability. Due to limitations in the number of output pins as well as area and power overhead constraints of internal trace buffer, only a small percentage of internal signals in the design can be observed during silicon execution. Furthermore, in order for a signal to be observed, the design must be instrumented a priori with appropriate control hardware that

Figure 1-1. Different phases of validation and testing in IC design flow

routes a signal to an observation point. It is therefore crucial to identify trace signals that maximize design visibility and debug information under the observability constraints.

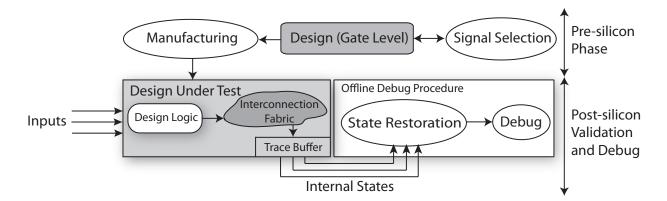

Figure 1-2 provides an overview of post-silicon validation and debug process. Signal selection and trace buffer design are done in pre-silicon phase. If an error occurs during post-silicon validation phase, the traced values of internal signals are dumped. During off-line trace analysis, a restoration procedure tries to reconstruct unknown signal states from the traced signal values. During off-line debug process both dumped signals and restored signals are used to locate the error. The number of signals that can be traced per cycle is limited to trace buffer width. In addition, the maximum number of values recorded per signal is limited to the trace buffer depth. Due to design overhead considerations, trace buffer size tends to be very small. In a million-gate design, a typical trace buffer width is 128 and depth is 2048. In other words, a  $128 \times 2048$  trace buffer can trace 128 signals (out of millions of possible signals) for 2048 cycles. Therefore, the primary objective is to select a small set of profitable signals that can maximize restoration performance. A major challenge in efficient signal selection is that the exploration space (number of potential alternatives) can be prohibitively large even for small circuits. For example, s35932 circuit of ISCAS'89 benchmarks suite has 1728 flip-flops. If the trace buffer width is 32, we need to choose 32 signals out of the total 1728 flip-flops. It is easy to observe that there are more than  $10^{69}$  such combinations. This makes exhaustive exploration infeasible<sup>1</sup>.

The focus of this dissertation is to reduce the overall effort of post-silicon validation and debug. The remainder of this chapter is organized as follows. First, we describe the basics of signal restoration which is an important concept in post-silicon validation. We then explain

$<sup>^{1}</sup>$  If each simulation for evaluating one combination takes only 1 second, more than  $10^{60}$  years is needed in order to find the best 32 trace signals in s35932 circuit using one single machine.

Figure 1-2. An overview of post-silicon validation flow

various challenges associated with post-silicon validation and our contributions to address them.

#### 1.1 Signal Restoration in Post Silicon Validation

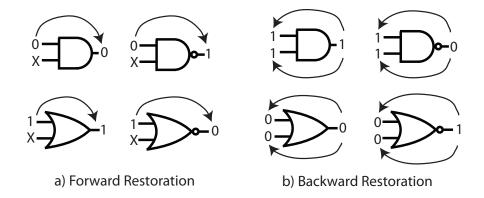

Restoration entails inferring values of untraced signal states from a sequence of traced signals sampled over a period of time. This is achieved using forward and backward propagation of signal values of circuit elements (e.g., gates, latches, etc.). Figure 1-3 illustrates forward and backward restoration for common logical gates. Forward propagation involves reconstructing the output of a circuit element from traced inputs. For example, if one of the inputs of the *OR* gate is '1', the output value would be '1'. If all the inputs are known, the unknown output can be definitely determined. On the other hand, backward propagation involves inferring input values from the observed output. For example, if the output of the *OR* gate is '0', both of the inputs would be '0'. Backward reconstruction might fail in certain scenarios. For example, if the output of a 2-input *OR* gate is '1' and one of the input has a known value of '1', the other input still cannot be reconstructed. During signal value reconstruction, forward and backward restoration are repeated for all the gates in the circuit until no more states can be restored. Restoration Ratio (RR), defined below, is a popular metric for measuring the quality of a set of selected trace signals.

$$\mbox{Restoration Ratio} = \frac{\mbox{Number of traced and restored signals}}{\mbox{Number of traced signals}}$$

13

Figure 1-3. Basic restoration rules for common logic gates

Consider the simple circuit shown in Figure 1-4 used in [3]. Suppose that the width of the trace buffer is 2 (*i.e.*, only two signals can be traced at any clock cycle), and the trace buffer depth is 8 (*i.e.*, selected signals are traced for 8 cycles). Suppose that A and C are selected as trace signals. Table 1-1 shows the signal states that can be restored using the traced values of A and C over eight cycles. In this example, 32 signal values can be restored (entries with '0' or '1' in the table) while 16 are traced (two signals for eight cycles, i.e.,  $2 \times 8 = 16$ ), yielding a restoration ratio of (32 + 16)/16 = 3.

#### 1.2 Challenges

There are many challenges in efficient post-silicon validation and debug. This section describes three important challenges that I have addressed in my dissertation.

Figure 1-4. A simple circuit to illustrate restorability

Table 1-1. Illustration of restored signals for the simple circuit shown in Figure 1-4

| Signal | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| Α      | 0       | 1       | 0       | 0       | 0       | 1       | 1       | 1       |

| В      | 0       | Χ       | 1       | 1       | 1       | Χ       | Χ       | Χ       |

| С      | 0       | 0       | 1       | 1       | 1       | 1       | 1       | 1       |

| D      | Χ       | 0       | 0       | 0       | 0       | 0       | 1       | 1       |

| Е      | Χ       | 0       | 0       | 1       | 1       | 1       | Χ       | Χ       |

| F      | Χ       | Χ       | 0       | 0       | 1       | 1       | 1       | 1       |

| G      | Χ       | 0       | Χ       | 0       | 0       | 0       | 1       | 1       |

| Н      | Χ       | 0       | Χ       | 0       | 0       | 1       | Χ       | Χ       |

Challenge 1: There is a limited number of signals to be traced which should be selected carefully in order to maximize the restoration ratio during the post silicon debug. Existing approaches either use some metrics based on the circuit structure to select the signals [3–6] or they use expensive simulations/restorations [7]. The former can sacrifice the restoration quality and the latter is not scalable if it is not done carefully, due to the prohibitive computation time requirements. An efficient selection algorithm is needed which can select trace signals to provide a high restoration ratio.

**Challenge 2:** As discussed in *Challenge 1*, metric-based selection techniques are fast and scalable but provide a low restoration performance. On the other side, simulation-based techniques provide a high restoration performance but generally are not scalable for large circuits. A scalable selection technique is needed which can be applied to large industry scale circuits.

Challenge 3: The use of scan chains in post-silicon debug has been extensively studied in [8, 9]. Ko et al. [10] proposed an architecture that divides trace buffer bandwidth into two parts, one for the trace signals and the other one for the scan signals. In order to find the most beneficial partitioning, they proposed an exhaustive exploration. However, exhaustive exploration is not practical in real designs with large number of flip-flops. Basu et al. [11] proposed an efficient algorithm that chooses trace and scan signals based on connectivity graph of flip-flops. They reduce the scan chain length by pruning the graph in each iteration. However, both of these techniques divide the signals in two extreme categories. One set of

Figure 1-5. Overview of research contributions

signals are traced every cycle. The other signals are dumped in a relatively large period. They do not consider other profitable fine-grained scenarios. An efficient fine-grained architecture is needed that shares the trace buffer bandwidth between several scan chains with different lengths to significantly improve restoration performance.

#### 1.3 Research Contributions

My research proposes novel techniques to address challenges in post-silicon validation and debug described in Section 1.2. The objective of my research is to develop efficient signal selection techniques as well as trace hardware architectures. The major contributions of my research are summarized as follows. Figure 1-5 highlights these contributions in the IC design methodology.

**ILP-based signal selection:** This contribution addresses the first challenge outlined in Section 1.2. Most existing signal selection techniques rely on a metric based on circuit structure. Simulation-based signal selection is promising but have major drawbacks in computation overhead and restoration quality. In this dissertation we propose an efficient simulation-based signal selection technique to address these bottlenecks. Our approach uses (1) bounded mock simulations to determine state restoration effectiveness, and (2) an ILP-based algorithm for refining selected signals over different simulation runs.

Efficient selection of fine-grained combination of trace and scan signals: This contribution addresses the first and third challenge outlined in Section 1.2. One of the key challenges in post-silicon validation is the limited observability of internal signals in manufactured chips. A promising direction to improve observability is to combine trace and scan signals - a small set of trace signals are stored every cycle, whereas a large set of scan signals are dumped across multiple cycles. Existing techniques are not very effective since they explore a coarse-grained combination of trace and scan signals. In this dissertation, we propose a fine-grained architecture that addresses this issue by using various scan chains with different dumping periods. We also propose efficient algorithms to select beneficial signals based on this architecture.

Scalable Trace Signal Selection using Machine Learning: This contribution addresses the first and second challenge outlined in Section 1.2. Structural analysis used by traditional signal selection techniques leads to poor restoration quality. In contrast, simulation-based selection techniques provide superior restorability but incur significant computation overhead. In this dissertation, we propose efficient signal selection techniques using machine learning to take advantage of simulation-based signal selection while significantly reducing the simulation overhead. Our approaches use (1) bounded mock simulations to generate training vectors set for the machine learning technique, and (2) train a machine learning model and apply it to the circuit to identify the most profitable signals set.

#### 1.4 Dissertation Organization

The dissertation is organized as follows. Chapter 2 describes background and the related work. Chapter 3 presents our ILP-based trace signal selection technique. Chapter 4 describes our fine-grained trace and scan signal architecture and corresponding selection techniques. Chapter 5 presents our scalable selection algorithms using machine learning techniques. Finally, Chapter 6 concludes the dissertation.

# CHAPTER 2 BACKGROUND AND RELATED APPROACHES

A primary problem for post-silicon debug is the limited observability of internal signals since the chip has already been fabricated. Once the signal states are known, they can be analyzed using techniques like failure propagation tracing [12] to identify the errors in the circuit. Koushanfar et al. [13] proposed a technique to obtain the internal states of a system using a concept called golden cut. However, their method is not applicable for post-silicon debug since it is difficult to stop execution of a process running on a chip and get all the current signal states. Formal analysis for post silicon debug proposed by De Paula [14] is not applicable to circuits with a large number of gates. Physical probing techniques were proposed by Nataraj et al. [15]. Decrease in feature size and growing complexity of IC designs have made it difficult to implement these techniques in practice. A method for validation of memory subsystem in CMPs was proposed by DeOrio et al. [16], where it only focuses on the memory subsystem. Scan based debugging techniques such as [17] are not appropriate since they require to stop the circuit functionality when the scan data is being written. This is particularly not beneficial when the functional errors are drastically apart. Double buffering [18] of scan elements helps to mitigate this problem, but with a large area penalty. Design-for-Debug (DfD) techniques have been used extensively to increase the observability of internal signals of the silicon. Generally this is performed by sampling the data which is stored in on-chip trace buffers. Various DfD techniques like embedded logic analyzer (ELA) [19] and shadow flip flops [18] have been proposed over the years for post-silicon debug. ELA can be used to probe into the chip and record some internal logic states. The trace is then recorded in an on-chip trace buffer. During debug, the contents of trace buffer is transferred to an offline debugger via some Joint Test Action Group (JTAG) interface.

The notion of restorability is based on the execution of the circuit on an input sequence; when the input sequence represents an on-field execution scenario for the circuit during post-silicon validation. However, signals must be selected *a priori* based on the circuit structure.

Heuristics for selecting signals need to comprehend and encapsulate overlaps and interactions between different signals, and anticipate how such interactions might affect restorability on-field — an intrinsically difficult task. In this chapter, we present the background and related work for trace signal selection techniques as well as other methodologies to improve the overall post-silicon debug effort.

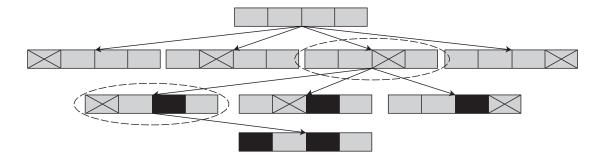

#### 2.1 Trace Signal Selection

Trace buffers have been widely studied in post-silicon debug [6, 20–24]. Existing signal selection approaches can be classified in two categories, metric-based (structural) and simulation-based. Approaches in the first category use greedy heuristic to iteratively select signals optimizing a metric based on the circuit structure [3–5]. They are relatively efficient in computation speed, but have poor restoration quality compared to simulation-based algorithms. Simulation-based algorithms are based on the intuition that if a set of signals works well for some random input vectors then it is also likely to provide high state reconstruction on other inputs and therefore a high restorability ratio. In particular, Chatterjee et al. [7] showed that mock simulations are more effective in identifying trace signals than metrics based on the circuit structure. Their approach involves an iterative removal process. They start with a set of candidate signals which is initialized with all flip-flops. In each iteration, their algorithm attempts to remove one of the signals which appears to be least important based on simulation results. The process continues until the number of remaining candidates equals to the trace buffer width. Figure 2-1 illustrates the approach for a sample circuit with a total of 4 flip-flops and a trace buffer of width 2. This selection technique is promising but it requires  $O(N^2)$  simulations where N is the number of flip-flops in the circuit. This makes their approach computationally expensive for large circuits. To address this issue, they propose a pre-processing phase namely pruning process, prior to running the algorithm. Basically, the pruning phase is the algorithm itself with less accuracy. The pruning phase reduces the initial candidate flip-flops set but still requires long signal selection time. In addition, it may sacrifice the signal selection quality. Li et al. [25] proposed a hybrid (metric-based

Figure 2-1. Simulation-based trace signal selection flow

and simulation-based) signal selection technique. However, to save selection time, [25] uses simulation for a small fraction of the signals and thereby sacrifices restoration performance. Ma et al. [26] proposed a selection technique based on a new metric called Pagerank which tries to maximize behavioral coverage during post-silicon debug. Zhu et al. [27] proposed a signal selection technique with the aim of facilitating the subsequent automated localization of faults using consistency-based diagnosis. BeigMohammadi et al. [28] proposed a signal selection method that selects combinational gates in addition to flip-flops in the circuit with the goal of further improving restoration capability.

To address the challenges of the simulation based approach proposed in [7], we present a top-down simulation-based technique in Chapter 3. Our approach has two components: (1) an iterative approach to signal selection based on mock simulations, and (2) a filtering scheme based on Integer-Linear Programming (ILP) to refine the selected set.

#### 2.2 Dynamic Signal Selection

Existing trace signal selection techniques focus on selecting a set of signals that are traced every cycle during the debug time. Prabhakar et al. [29] proposed a technique where they alternate between two set of signals every other cycle based on implication-based correlation. Liu et al. [30] proposed a multiplexed signal selection for error detection using a heuristic based on error-visibility metric. Basu et al. [31] proposed a dynamic selection approach where it considers both spatial and temporal distribution of errors. Han et al. [32] proposed a dynamic signal selection based on the characteristic of the circuit under test to maximize the visibility.

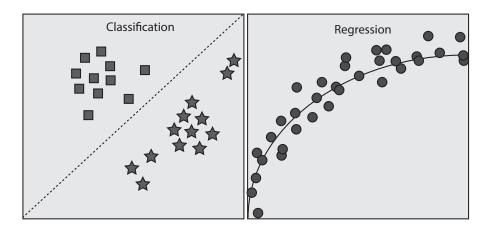

Figure 2-2. Two different type of supervised learning

Zhu et al. [33] proposed a dynamic selection technique which utilizes machine learning for classification of the groups of signals that are likely to trigger different faults.

#### 2.3 Supervised Learning and Prediction

Supervised learning is a technique of inferring an unknown output for an input vector using a set of training examples consisting of pairs of input vectors and corresponding known outputs. There is two main categories for supervised learning in machine learning, classification and regression. Classification is predicting whether an element belongs to a set of discrete values (or classes) whereas, regression is predicting the value for a continuous function. An example for classification is classifying an email as spam or legitimate email based on some features of its content and meta data (feature vector). On the other side, predicting the price of a house based on its features like location, size, and age (feature vector) would be a regression prediction as the price is a continues value. In fact, classification is a special case of regression where each class is assigned to a range of values (or probabilities) of the prediction function. This is illustrated in Figure 2-2. The classification predictor divides the outputs to different classes, square and star. On the other hand, the regression is a continuous function trying to fit the best line passing through the inputs and outputs. In Chapter 5, we develop novel signal selection techniques based on regression to retain (and improve upon) the restoration quality of simulation-based signal selection with a drastically faster selection time.

#### 2.4 Trace Data Compression

To increase the amount of data that can be stored in a trace buffer while keeping the trace buffer size constant, trace compression techniques have been proposed [34–37], which compress the trace data before storing them into trace buffer. This enables us to observe more trace data while keeping the trace buffer size constant. The trace buffer has two parameters, width and depth. Width refers to the number of signals whose states can be stored every cycle, while depth refers to the number of cycles over which the trace is stored. Existing trace compression approaches differ in terms of compression objectives. While [36] compresses the width of the trace buffer, [34, 35] compress the depth. Muthyala et al. [38] proposed a feedforward techniques for improving the compression in scan based decompressors.

#### 2.5 Observability-Aware Test Generation

A major problem in post-silicon validation is that the regression tests may not be observability-aware. While the tests are likely to activate the errors, but there effects may not propagate to the observable points (e.g., trace signals). For example, if the result of a test affects a signal and it is not observable, it is difficult to determine whether the test has executed as expected.

Soft errors and crosstalk faults are two major electrical errors found in a fabricated SoC. Effect of soft errors on memory devices had been studied as early as in 1979 by May et al. [39]. Over the years, researchers [40–42] have studied the various aspects of soft errors. Sanyal et al. [43, 44] have proposed different methods for directed test generation for soft errors. However, these approaches are not designed for post-silicon validation purposes, that is, they assume all the output signals of a logic block are visible. However, during post-silicon validation, since the chip is fabricated, observing the output signals of every component may not be feasible since these components can be embedded in an SoC. The only observable points would be the trace signals. The test generation algorithms need to be modified to take this into account. Crosstalk faults occur when two lines in a circuit are so near that their mutual capacitance affects their state. Effects of crosstalk faults on digital circuits [45–47] have been studied

22

extensively. Existing test generation algorithms for crosstalk faults [48–50] suffer from the same problem as the corresponding test generation algorithms for soft errors - that is, they are not suitable for application in post-silicon validation due to limited observability through trace signals. There has also been recent approaches [51, 52] proposed which exploit an on-chip hardware component to generate real-time stimuli to satisfy the functionally-compliant stimuli requirements.

In addition to soft errors and Crosstalk faults, there has been several works on detecting functional errors. Adir et al. [53] proposed an approach to detect functional errors using random test generation. On the other side, directed test generation techniques [54, 55] try to generate tests that target a specific functional scenario. However, they are effective only if the list of the bugs are available a priori. Farhmandi et al. proposed a test generation approach [56] that is guaranteed to activate unknown bugs. Their technique also addresses the scalability concern of existing bug localizations approaches [57–59] with a faster bug localization. However, none of these approaches consider observability (trace signals) during test generation. Recently, Farahmandi et al. [60] proposed a framework for observability-aware test generation using transaction-level models.

#### 2.6 Post-silicon Debug Techniques

Trace buffers are used to capture the signals during post-silicon validation. Recent works [34, 35, 61, 62] has been proposed with the goal of reducing the validation time by reducing the debug iterations. The main idea is that it is not necessary to store all the cycles specially for those signals that can be restored using simulation or those that are most likely from a non-buggy cycle. Their approach involve a multiple-step debug session where it allows the debugger to expand the visibility window. Effectively, it allows to zoom in and zoom out during the debugging session by storing a signature of trace signal values in a larger block of cycles. This means, data might get lost as we compress several bits in a few parity bits. In fact, during the debug session we do not know which cycles are the erroneous ones to store and we rely on a multiple-step offline software analysis to find those based on the input. There has also

been other approaches [63–65] proposed where they use trace data for detecting electrical errors (such as bit-flips), in addition to functional design errors. Goossens et al. [66] proposed a debug technique where it focuses on observing the communications among the IP blocks and mapping it to the transactions. Similar approaches have been proposed in [67, 68]. Zheng et al. [69] proposed a technique to infer system-level transactions from trace data to have a better high-level understanding of the system during the debug.

#### 2.7 Combination of Trace and Scan Signals

Scan based debugging is widely used in manufacturing test. It is used to detect the fabrication defects in the chip. It would be beneficial to use scan dump in post-silicon debug. The problem is that the data can only be dumped in scan or debug mode. During these modes the circuit execution needs to be interrupted. This prevents real-time observability of the internal states. Enhanced scan chains are proposed in [10] to address this issue in which shadow flip-flops are used to form a shadow scan chain. Shadow flip-flops enable storing scan signals without interrupting normal execution of the circuit.

The use of scan chains in post-silicon debug has been extensively studied in [8, 9]. Ko et al. [10] proposed an architecture that divides trace buffer bandwidth into two parts, one for the trace signals and the other one for the scan signals. In order to find the most beneficial partitioning they proposed an exhaustive exploration. However, exhaustive exploration is not practical in real designs with large number of flip-flops. Basu et al. [11] proposed an efficient algorithm that chooses trace and scan signals based on connectivity graph of flip-flops. They reduce the scan chain length by pruning the graph in each iteration. However, both of these techniques divide the signals in two extreme categories. One set of signals are traced every cycle. The other signals are dumped in a relatively large period. They do not consider other profitable fine-grained scenarios. It would be beneficial if we divide the signals in a large number of categories in terms of dumping period. This enables us to select a promising signal with a profitable dumping period. In Chapter 4, we propose an efficient fine-grained architecture that shares the trace buffer bandwidth between several scan chains with different

dumping periods. We also propose two different signal selection algorithms which can be used based on hardware constraints. Our signal selection algorithms assign the signals to different scan chains in order to maximize the number of states that can be restored.

# CHAPTER 3 TRACE SIGNAL SELECTION USING AUGMENTATION AND ILP TECHNIQUES

In this chapter, we describe our ILP-based signal selection which is inspired by simulation-based signal selection techniques, but includes a refinement technique to address the weaknesses of previous simulation-based approaches. Before presenting the technical details of our approach, we motivate it by comparing its results using illustrative examples with state-of-the-art metric-based and simulation-based approaches, *viz.*, Basu *et al.* [3] and Chatterjee *et al.* [7]; these experiments expose some key features of our approach which we then discuss.

For the circuit in Figure 1-4, Basu *et al.* [3] select signals A and C, thus yielding the restoration ratio of 3 as shown in Table 3-1. On the other hand, both our approach and the simulation-based approach of Chatterjee *et al.* [7] selects signals A and B. The corresponding restorability calculations are shown in Table 3-2. From the table, 40 states are restored from tracing 16 states, yielding a restoration ratio of 3.5.

On the other hand, to illustrate the distinction between our approach and Chatterjee et al. [7] consider the circuit in Figure 3-1. For a trace buffer width of 2, Chatterjee et al. [7] produce signals B and C. From Table 3-3, this leads to a restoration of 13 states from a total of 16 traced states, yielding a restoration ratio of 1.81. On the other hand, our approach selects signals C and K. From Table 3-4, this allows restoration of 18 states from 16 traced states, resulting in a restoration ratio of 2.13.

Table 3-1. Illustration of restored signals for the simple circuit shown in Figure 1-4

| Signal | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| Α      | 0       | 1       | 0       | 0       | 0       | 1       | 1       | 1       |

| В      | 0       | Χ       | 1       | 1       | 1       | Χ       | Χ       | Χ       |

| С      | 0       | 0       | 1       | 1       | 1       | 1       | 1       | 1       |

| D      | Χ       | 0       | 0       | 0       | 0       | 0       | 1       | 1       |

| E      | Χ       | 0       | 0       | 1       | 1       | 1       | Χ       | Χ       |

| F      | Χ       | Χ       | 0       | 0       | 1       | 1       | 1       | 1       |

| G      | Χ       | 0       | Χ       | 0       | 0       | 0       | 1       | 1       |

| Н      | Χ       | 0       | Χ       | 0       | 0       | 1       | Χ       | Χ       |

Table 3-2. Restored signals for circuits in Figure 1-4

| Signal | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| Α      | 0       | 1       | 0       | 0       | 0       | 1       | 1       | 1       |

| В      | 0       | 0       | 1       | 1       | 1       | 0       | 0       | 0       |

| С      | Χ       | 0       | 1       | 1       | 1       | 1       | 1       | 1       |

| D      | Χ       | 0       | 0       | 0       | 0       | 0       | 1       | 1       |

| Е      | Χ       | 0       | 0       | 1       | 1       | 1       | 0       | 0       |

| F      | Χ       | Χ       | 0       | 0       | 1       | 1       | 1       | 1       |

| G      | Χ       | 0       | Χ       | 0       | 0       | 0       | 1       | 1       |

| Н      | Χ       | 0       | 0       | 0       | 0       | 1       | 0       | 0       |

Figure 3-1. Example circuit to compare our approach with Chatterjee et al. [7]

It is illuminating to understand the source of the differences between the different approaches on these simple examples. The high restoration ratio achieved by both our approach and that of Chatterjee *et al.* [7] for the circuit in Figure 1-4 represents a general trend of superior signal quality achieved by simulation-based selection techniques; our observations here match the conclusions of Chatterjee *et al.* [7] as well. The comparison with Chatterjee *et al.* [7] for the circuit in Figure 3-1 is more interesting. Their approach is based on *greedy elimination*: starting with the set of all signals, they iteratively remove signals one at a time. In each iteration the objective is to select a candidate signal whose elimination minimizes the number of states which become unrestorable as a result; this signal is then eliminated and the algorithm iterates. The problem with this approach is that the candidate computation

Table 3-3. Restored signals from Chatterjee et al. [7] for the circuit in Figure 3-1

| Signal | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| Α      | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | X       |

| В      | 0       | 0       | 1       | 1       | 0       | 0       | 1       | 0       |

| C      | 0       | 1       | 1       | 1       | 0       | 1       | 1       | 0       |

| D      | Χ       | Χ       | 1       | 1       | 1       | Χ       | 1       | 1       |

| E      | Χ       | Χ       | Χ       | 0       | 0       | 1       | Χ       | 0       |

| F      | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       |

| K      | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       |

| L      | Χ       | 0       | Χ       | Χ       | Χ       | 0       | Χ       | Χ       |

| M      | Χ       | Χ       | 0       | Χ       | Χ       | Χ       | 0       | Χ       |

Table 3-4. Restored signals using our method for the circuit in Figure 3-1

| Signal | Cycle 1 | Cycle 2 | Cycle 3 | Cycle 4 | Cycle 5 | Cycle 6 | Cycle 7 | Cycle 8 |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| Α      | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       |

| В      | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       |

| С      | 0       | 1       | 1       | 1       | 0       | 1       | 1       | 0       |

| D      | Χ       | Χ       | 1       | 1       | 1       | Χ       | 1       | 1       |

| E      | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       |

| F      | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       | Χ       |

| K      | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 1       |

| L      | Χ       | 0       | 0       | 0       | 0       | 0       | 0       | 1       |

| M      | Χ       | Χ       | 0       | 0       | 0       | 0       | 0       | 0       |

assumes that all the remaining signals are available for state restoration, an assumption that is flawed precisely by virtue of the iterative elimination algorithm itself. Thus it is possible that a profitable signal s is eliminated in an early iteration when the states reconstructible from s can also be restored by other signals available at that iteration; however, these states can no longer be reconstructed when a subsequent iteration eliminates other signals. In the example, the signal K is eliminated in an early iteration since the states restorable from K can be restored without K as long as the signal L is available; however, when a subsequent iteration eliminates L as well, the set of states that can be restored gets drastically reduced.

#### 3.1 Augmentation-based Selection

Our algorithm exploits the advantages of simulation-based signal selection while avoiding the drawbacks discussed above. Figure 3-2 illustrates the framework. We apply an iterative

approach based on augmentation rather than elimination. In particular, we maintain a set S of signal candidates (initially empty), which we "grow" at each iteration by identifying the most promising signal based on mock simulations; the objective is to maximize the set of states that can be restored from the signals in the candidate set. The key observation here is that in this approach restorability of the candidate set is never over-estimated at any iteration since each member of S is guaranteed to be in the final trace selection set. Furthermore, note that the number of iterations in this approach is bounded by buffer size, which is very small precisely because of the observability limitation in post-silicon validation. On the other hand, the number of iterations in the elimination-based selection is bounded by the number of signals which can be large. Thus our approach achieves much better run-time performance compared to the elimination-based selection.

Figure 3-2. Proposed signal selection process

Our second observation is that any selection algorithm based on random simulation is susceptible to perturbations based on the randomness in the input vectors. To eliminate the influence of randomness, our approach makes use of multiple simulation runs using an ILP-based refinement algorithm to consolidate the results from these runs.

#### 3.1.1 Augmentation-based Signal Selection

We first describe our augmentation-based selection algorithm; we will discuss the ILP-based refinement in the next subsection. Algorithm 1 outlines the major steps of the signal selection process. The inputs of the algorithm are the *circuit*, *trace buffer width* (w), and *the number of cycles in mock simulations* (c). To understand the workings of the algorithm we need two key concepts: *restoration influence* and *restoration difference*.

Given a set of candidate signals s, an input vector l, and the number of simulation cycles c, we define the *Restoration Influence RI*(s, l, c), as the total number of states that can be restored if we do a mock simulation over c cycles using input vector l and the signals set S. The *restoration difference* between two candidates  $s_1$  and  $s_2$  with respect to l and c, denoted by  $RD(s_1, s_2, l, c)$ , is then given by the following formula:

$$RD(s_1, s_2, l, c) = RI(s_1, l, c) - RI(s_2, l, c)$$

```

Data: circuit, w, c

Result: Selected set of signals S

Create flip-flops graph of circuit;

Create list of selected signals S

while |S| < w do

Generate a random input vector I;

foreach flip-flop f that is not in the S do

Calculate RD(S \cup \{f\}, S, I, c);

end

Find flip-flop f with maximum RD. If two or more flip-flops have same RD, find the one with higher connectivity;

Add f to the list S;

end

return S;

```

**Algorithm 1:** SelectSignals Procedure

Informally, for a given c-cycle mock simulation I, the restoration difference between two candidate signal sets  $s_1$  and  $s_2$  measures the observability improvement achieved by selecting  $s_2$  over  $s_1$ . In particular, if  $s_2 = s_1 \cup \{f\}$  for some design signal f, then it measures the observability improvement achieved by augmenting  $s_1$  with f. Algorithm 1 is a greedy algorithm that uses this metric to iteratively grow the set S of currently selected signals. At each iteration, it (1) performs a new simulation for c cycles using a random input vector I, (2) computes the restoration difference between S and  $S \cup \{f\}$  for each design signal f, and (3) augments S with the signal that maximizes the restoration difference. If two or more

signals have identical restoration difference, then the tie is broken in favor of the signal that has the highest connectivity.<sup>1</sup> The process is continued until *w* signals have been selected.

#### 3.1.2 ILP Optimization

Experiments show that most of the selected trace signals are identical in different runs of our signal selection. However, in any simulation-based signal selection approach, signals may be different in different runs depending on generated random input vector seed. The goal of our refinement algorithm is to eliminate the influence of randomness and also to cover more states of the circuit through selected signals. To do so, we use multiple runs of the signal selection algorithm which are then processed by ILP to select the best signal set among all outcomes.

```

Data: circuit, w, c, p

Result: The matrices associated to the ILP problem

Create S[1..p][1..w] and R[1..p][1..w];

Create k and j, initialize to 1;

Create list of all selected signals A

initially empty ;

Create list of selected signals S

initially empty ;

while k \le p do

T = Signal selection algorithm with (circuit, w, c);

Generate a random input vector I;

j = 1:

foreach flip-flop f in the T do

S[k][j] = f;

A = A \cup \{f\};

RD_f = RD(T, T - \{f\}, I, c);

R[k][j] = RD_f;

end

k++;

return A, S, and R;

```

Algorithm 2: InitializeMatrices Procedure

<sup>&</sup>lt;sup>1</sup> The connectivity of a flip-flop is the number of flip-flops connected to it through other combinational gates in both backward and forward directions.

To perform the refinement, we first create ILP formulation matrices from the signal selection algorithm. Algorithm 2 outlines the steps involved. The inputs of the algorithm are the *circuit*, *trace buffer width* (w), the number of cycles in mock simulations (c), and refinement precision (p). The refinement precision specifies the number of runs of the signal selection algorithm used in the refinement process. The algorithm returns two matrices S and R, and a set A, which are then used as the basis of the ILP optimization. A is the set of all flip-flops selected in the p runs of our selection algorithm. The matrices S and R record the importance of the selected flip-flops in state reconstruction: S[k][j] records the j-th selected flip-flop in the k-th run of our selection algorithm; R[k][j] records the number of states that is lost in the mock simulation corresponding to the k-th run if S[k][j] is removed from the final selected set. The algorithm executes p runs of our selection algorithm, filling out the entries S[k][j] and R[k][j] at the k-th run. Recall that the perturbation caused to the selection set is typically small. Thus, for the set T of flip-flops computed in the k-th run and any  $f \in T$ , most of the signals in  $T - \{f\}$  end up in the final selected signal set; thus, the value of R[k][j] is a reliable estimate of the importance of flip-flop S[k][j].

Once the required matrices are initialized, we can model our refinement process as an ILP optimization problem in a fairly standard manner. For each flip-flop in A, we create a variable which can be 0 or 1.  $A_i = 1$  indicates that  $A_i$  is eliminated;  $A_i = 0$  indicates that it is not removed and therefore exists in final trace signals set. Note that since A is a cumulative superset of all selected flip-flops during p runs, for each  $1 \le i \le p$  and  $1 \le j \le w$ , we have  $S[i][j] \in A$ . Equation 3–1 shows the objective function which should be minimized.  $L_i$  is the number of states that is lost in  $i_{th}$  run, based on signal assignments in A. The aim is to minimize the total number of lost states in all the runs.

$$min: \sum_{i=1}^{p} L_i \tag{3-1}$$

Equation 3–2 shows how  $L_i$  is calculated. Recall that S[i][j] is the assignment of signal j in A (which is 0 or 1), and R[i][j] is the number of states that is lost in i-th run if j-th signal

is removed (i.e., is equal to 1). Therefore,  $L_i$  is the total number of states that is lost due to removed flip-flops of i-th run.

$$L_1 = \sum_{i=1}^{w} S[1][i] * R[1][i] ..., L_p = \sum_{i=1}^{w} S[p][i] * R[p][i]$$

(3-2)

The constraints of ILP optimization problem are shown in Equation 3–3. Recall that A is the superset of all selected signals in different runs. However, |A| may be larger than w as some selected signals may be different during signal selection runs. It means |A| - w signals must be removed from A. These signals are removed in such a way that the total number of lost states in all runs is minimized. The remaining w flip-flops in A which are assigned to 0 correspond to the final trace signals set.

$$\sum_{i=1}^{|A|} A_i = |A| - w$$

$$A_1, A_2, ..., A_{|A|} \in \{1, 0\}$$

(3-3)

#### 3.1.3 Complexity and Scalability

Simulation of large industrial designs incurs high cost in running time. Indeed, simulation time is the primary bottleneck in the usability of simulation-based signal selection on large-scale designs. Therefore, a good metric of the complexity of such algorithms is the number of mock simulations required in the computation. Note that although our approach involves ILP-based optimization, the running time for solving the ILP in practice is still negligible compared to the time for mock simulations. The reason is that the perturbation caused by randomization in simulations in practice to the selected set of signals is small, so that there is a large overlap between the signals selected at different runs. Thus, the selected set A of flip-flops over all the different runs in our ILP-based refinement is of the order of the width of the trace buffer, independent of the number p of iterations of the selection algorithm actually performed. Consequently, we compute the complexity of our algorithm in terms of the number of required mock simulations.

Assume that there are N flip-flops in the circuit and the trace buffer width is w. Number of needed simulation in each run of signal selection algorithm is N + (N-1) + ... + (N-w+1). Note that N >> w for large circuits, since the trace buffer size is bounded by the observability limitations. The complexity of Algorithm 1 is thus  $\theta(Nw)$ . Algorithm 2 consists of a main loop which runs signal selection algorithm followed by w additional simulations to fill in matrix R. Consequently, each iteration needs  $\theta(Nw) + \theta(w) = \theta(Nw)$  simulations. Therefore, the complexity of our algorithm is  $p * \theta(Nw) = \theta(Npw)$ . However, our experiments show that in practice  $p \ll N$  is enough to cover most of the input vectors. Consequently, in most cases, our algorithm requires fewer simulations than the previous simulation-based approach of Chatterjee et al. [7], which has a complexity of  $O(N^2)$  — with the lower bound of  $\Omega(N^2/d_{step})$  which is still computationally expensive since  $N>>d_{step}$  in large industry-scale circuits ( $d_{step} = 50$  in their experiments). On the other hand, the hybrid approach [25] uses simulation/restoration computation only for top k% of the candidate signals, (where k=5 in their experiments). The complexity of their approach is O(kwN) where w is the trace buffer width. Note that once the parameters are fixed, both our approach and the hybrid approach have the same asymptotic complexity  $\theta(N)$ , with different constant coefficients.

In addition, not only all the simulations in each iteration of our selection algorithm are independent, but the iterations of initialization algorithm are also independent tasks. This makes our approach scalable for very large industry-level circuits by running them in parallel in a multi-processor environment.

#### 3.2 Experiments

#### 3.2.1 Experimental Setup

In order to investigate the effectiveness of our proposed approach, we have developed a cycle-accurate simulator for ISCAS'89 benchmarks using C++. Our simulator also conducts restoration in both forward and backward directions. The simulator iterates on the unknown signals queue and attempts to restore them leveraging both forward and backward techniques. This process terminates when it is not possible to restore any more states. In addition, we

checked the correctness of our simulator by comparing its output with the output of Verilog simulation of the identical circuits using *Icarus Verilog* [70]. We also used *Ip\_solve* 5.5 [71] to solve the ILP optimization part of our approach.

In the results reported below, the comparisons with related work [7, 25] are based on our implementation of their results. The reason is that their reported results used their own synthesized/optimized version of the ISCAS'89 benchmarks, while we used the standard, publicly available versions. Moreover to make the comparison fair for comparing restorability, identical input vectors should be used in all the approaches. We used the same parameters c=64 and PT=95% as reported in Chatterjee et al. [7]. In addition, we used the same parameters M=64, k=5%, and an initialization simulation of 10K cycles as reported in Li et al. [25]. We also used c=32 and p=6 for our approach in our experiments. Our experiments demonstrate that restoration ratio shows no improvement for p>6 in the set of used benchmarks. After signal selection and for reporting the restoration ratios, we fed the simulator with 100 sets of random input vectors and noted the average restoration ratios for the selected set of signals. However, we forced the circuits to operate in their normal mode by fixing the relevant control (reset) signals, while assigning random values to all the other inputs. The control signals include active low reset signals RESET in s35932 and g35 in s38584 which was set to 1 in our experiments. To make the comparison fair, these random input vectors are different from those which are used in signal selection process.

#### 3.2.2 Results

#### 3.2.2.1 Restoration quality

Table 3-5 presents the restoration ratios of our approach compared with previous techniques [7, 25] using the ISCAS'89 benchmarks. The trace buffer sizes used in our experiment are  $8 \times 4k$ ,  $16 \times 4k$ , and  $32 \times 4k$ . The corresponding restoration ratio for each technique is reported. The last column indicates the percentage of improvement using our approach compared with the best (shown in bold) result provided by existing approaches. The results indicate that our approach performs significantly better in most cases; in particular we

Table 3-5. Restoration ratios using our approach compared with existing selection approaches

| Circuit | Flip-flops | Buffer<br>Width | Simulation-based [7] | Hybrid [25] | Our Ap-<br>proach | Improvement over the best |

|---------|------------|-----------------|----------------------|-------------|-------------------|---------------------------|

|         |            | 8               | 13.41                | 13.32       | 14.63             | 9.1%                      |

| s5378   | 179        | 16              | 7.35                 | 7.26        | 9.26              | 26.0%                     |

|         |            | 32              | 4.47                 | 4.27        | 5.11              | 14.3%                     |

|         |            | 8               | 13.98                | 14.58       | 15.97             | 9.5%                      |

| s9234   | 228        | 16              | 8.30                 | 8.55        | 9.32              | 9.0%                      |

|         |            | 32              | 4.46                 | 4.46        | 5.53              | 24.0%                     |

|         |            | 8               | 26.33                | 27.38       | 45.89             | 67.6%                     |

| s15850  | 597        | 16              | 19.89                | 20.65       | 25.82             | 25.0%                     |

|         |            | 32              | 13.19                | 13.19       | 13.97             | 5.9%                      |

|         |            | 8               | 35.52                | 39.21       | 52.22             | 33.2%                     |

| s13207  | 669        | 16              | 20.13                | 22.47       | 34.89             | 55.3%                     |

|         |            | 32              | 11.25                | 12.52       | 16.37             | 30.8%                     |

|         |            | 8               | 19.73                | 25.87       | 159.1             | 515.0%                    |

| s38584  | 1452       | 16              | 28.39                | 29.01       | 48.39             | 66.8%                     |

|         |            | 32              | 32.45                | 34.62       | 44.46             | 28.4%                     |

|         |            | 8               | 29.23                | 51.01       | 53.47             | 4.8%                      |

| s38417  | 1636       | 16              | 17.02                | 19.22       | 26.87             | 39.8%                     |

|         |            | 32              | 15.14                | 13.25       | 17.22             | 13.7%                     |

|         |            | 8               | 132.00               | 139.52      | 185.1             | 32.7%                     |

| s35932  | 1728       | 16              | 67.45                | 71.36       | 93.2              | 30.6%                     |

|         |            | 32              | 34.63                | 35.08       | 47.13             | 34.4%                     |

achieve improvement in restoration performance is up to 515% (in *s38584*). Note however that the restoration ratio is heavily dependent on the circuit structure, and such high restoration in isolated cases may be an anomaly. Nevertheless, our approach performs better on most cases, with an improvement of 51.23% in restoration quality. Compared to original simulation-based signal selection [7], our fine-grained pruning reduces the chance of removing effective flip-flops prior to selection itself. On the other hand hybrid selection [25] incorporate simulations for only top 5% of the candidate flip-flops, which sacrifices the precision of the selection process; our approach performs better by addressing this weakness through refinement.

#### 3.2.2.2 Selection time

In addition to restoration ratio, we compared the runtime between our approach and Chatterjee *et al.* [7]. Figure 3-3 illustrates the selection time of our approach compared and normalized to [7] using different ISCAS'89 benchmarks. Since selection complexity of [7] is

Figure 3-3. Selection times of our approaches compared and normalized to Chatterjee et al. [7]

$O(N^2)$  ( $\Omega(N^2/50)$ ) in the best case) and ours is  $\theta(Npw)$ , as expected, for smaller benchmarks where pw is comparable to or larger than N our approach takes comparable time or longer than [7] (for example s5378 benchmark and buffer width of 16 and 32 respectively). However, our approach demonstrates consistent speed-up for larger benchmarks (s15850, s13207, s38584, s38417, and s35932). The reason is that even after pruning phase of [7], number of conducted simulations in [7] is significantly larger than our approach. In fact, once p and w are fixed, our approach grows linearly with respect to number of flip-flops in circuit. In short, our approach not only produces better restoration quality, but also it is more feasible in terms of selection runtime in large circuits. This makes our approach a better fit for large-scale industry circuits where N >> pw. Our signal selection time speed-up is up to 127.6X (in s38417 with buffer width of 8) and 12.9X on average. Note however that the hybrid approach of Li et al. [25] also reports significant speed-up over simulation-based techniques. However, their runtime results are reported for a multi-threaded implementation running on a specific quad-core machine, and are difficult to reproduce in our framework to provide a fair comparison.

## 3.3 Summary

Post-silicon validation is an expensive phase in the production of integrated circuits, and crucially depends on signal selection to effective use of the limited available observability. Thus it is critical to develop signal selection techniques that provide high state reconstruction and can scale to large industrial designs. Existing metric-based signal selection techniques are computationally efficient, but often yield signals with poor restorability; simulation-based techniques, while superior in restoration quality suffer from major computational drawbacks.

We presented a simulation-based signal selection technique that yields signals with higher restorability than current approaches while still being computationally efficient. Our key contribution is the observation that simulation-based signal selection can be significantly improved by augmentation through ILP-based refinement, together with the insights to smoothly integrate the augmentation phase into the selection framework resulting in a unified scalable infrastructure. Our experiments demonstrate that our approach provides up to 515% (51.23% on average) improvement in restoration ratio compared to existing signal selection techniques.

# CHAPTER 4 EFFICIENT COMBINATION OF TRACE AND SCAN SIGNALS