# TEST GENERATION FOR SYSTEM-ON-CHIP SECURITY VALIDATION

Ву

YANGDI LYU

A DISSERTATION PRESENTED TO THE GRADUATE SCHOOL

OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT

OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

UNIVERSITY OF FLORIDA

2020

#### **ACKNOWLEDGMENTS**

Firstly, I would like to express my sincere appreciation to my advisor, Prof. Prabhat Mishra, who provided the persistent support and guidance for my Ph.D. study. His patience, motivation and immense knowledge helped me in all aspects of research and writing this dissertation. He is the person who made my Ph.D. research and this dissertation come true.

Besides my advisor, I would like to thank the rest of my Ph.D. committee members (Prof. Sartaj Sahni, Prof. My Thai, and Prof. Swarup Bhunia) for their constructive recommendations and insightful critiques. Their diverse expertise and knowledge helped me improve the quality of my research and this dissertation.

I thank my fellow labmates: Yuanwen Huang, Farimah Farahmandi, Subodha Charles, Alif Ahmed, Zhixin Pan, Daniel Volya, Hasini Witharana, and Jonathan Cruz. It was my great pleasure to collaborate with them.

Last but not least, I sincerely acknowledge the support and great love of my parents, my wife and my son. This dissertation would not be possible without their unconditional support and love. I would like to offer my special appreciation to my wife, Xiaojie, who contributes a lot to the family and encouraged me to make the decision to start my Ph.D. Our happy family and the beautiful UF campus have made the five-year doctoral journey so delightful. I dedicate this dissertation to them.

# TABLE OF CONTENTS

|      |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | page                                               |

|------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| ACKI | NOW                                           | LEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 3                                                |

| LIST | OF T                                          | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 8                                                |

| LIST | OF F                                          | FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 9                                                |

| ABS  | TRAC                                          | т                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 12                                               |

| CHA  | PTER                                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    |

| 1    | INTE                                          | RODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 13                                               |

|      | 1.1<br>1.2<br>1.3<br>1.4                      | SoC Validation Methods  1.1.1 Formal Methods  1.1.2 Simulation-based Validation  1.1.3 Side-channel Analysis  SoC Security Validation Challenges  1.2.1 A Wide Variety of Vulnerabilities  1.2.2 Controllability and Observability  1.2.3 Lack of Effective and Scalable Validation Techniques  Research Contributions  Dissertation Organization                                                                                                                                                           | 17<br>18<br>18<br>19<br>20<br>20<br>21             |

| 2    | BACI                                          | KGROUND AND RELATED WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 30                                               |

|      | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | SoC Security Validation using Formal Methods SoC Security Validation using Simulation-based Validation 2.2.1 Random/Constrained-Random Simulation 2.2.2 Directed Test Generation using Formal Methods 2.2.3 Statistical Methods 2.2.4 Concolic Testing 2.2.4.1 Concolic Testing of Software Designs 2.2.4.2 Concolic Testing of Hardware Designs SoC Security Validation using Side-channel Analysis 2.3.1 Dynamic Current based Side-Channel Analysis 2.3.2 Path Delay based Side-Channel Analysis Summary | 30<br>31<br>31<br>32<br>35<br>36<br>36<br>37<br>37 |

| 3    | SYST                                          | TEM-ON-CHIP SECURITY ASSERTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 41                                               |

|      | 3.1                                           | Assertion-based Validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42<br>43<br>43<br>44                               |

|      |                                               | 3.2.1 Permissions and Privileges                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 44                                               |

|   |      | 3.2.2    | Resource Management                   | 45     |

|---|------|----------|---------------------------------------|--------|

|   |      | 3.2.3    | Illegal States and Transitions        | 45     |

|   |      | 3.2.4    | Buffer Issues                         | 45     |

|   |      | 3.2.5    | Information Leakage                   | 45     |

|   |      |          |                                       | 46     |

|   |      | 3.2.7    | Malicious Implants                    | 46     |

|   | 3.3  |          |                                       | 46     |

|   |      |          | ·                                     | 46     |

|   |      |          |                                       | 47     |

|   | 3.4  |          |                                       | 49     |

|   |      |          |                                       | 5(     |

|   |      |          |                                       | 51     |

|   |      |          |                                       | 51     |

|   |      |          |                                       | 52     |

|   |      |          |                                       | 54     |

|   |      |          |                                       | 5<br>5 |

|   | 3.5  |          |                                       | 56     |

|   | 5.5  | Julillia | 'y                                    | ,      |

| 4 | SCA  | LABLE (  | CONCOLIC TESTING OF RTL MODELS        | 58     |

|   | 4.1  | Overvie  |                                       | 59     |

|   |      | 4.1.1    | Modeling of Targets                   | 60     |

|   |      | 4.1.2    | Overview                              | 6(     |

|   | 4.2  |          |                                       | 61     |

|   |      | 4.2.1    | RTL Code Instrumentation              | 61     |

|   |      | 4.2.2    | Contribution-aware Edge Realignment   | 63     |

|   |      | 4.2.3    | Distance Computation                  | 67     |

|   |      | 4.2.4    | Path Exploration                      | 69     |

|   |      |          | 4.2.4.1 Dynamic Distance Update       | 7:     |

|   | 4.3  | Optimiz  | zations for Covering Multiple Targets | 72     |

|   |      |          |                                       | 73     |

|   |      |          |                                       | 75     |

|   | 4.4  | Experin  | nents                                 | 77     |

|   |      | 4.4.1    | Experimental Setup                    | 77     |

|   |      |          |                                       | 77     |

|   |      |          |                                       | 80     |

|   |      |          |                                       | 82     |

|   |      |          |                                       | 84     |

|   | 4.5  |          |                                       | 84     |

| 5 |      |          |                                       | 86     |

| J | I E3 |          |                                       |        |

|   | 5.1  |          |                                       | 88     |

|   | 5.2  |          |                                       | 89     |

|   |      | 5.2.1    | Simplified Abstract Syntax Tree       | 9(     |

|   |      | 5.2.2    | Adjust AST with Timing                | 91     |

|   |     | 5.2.3 Conversion of AST to Branch Target                         | 92  |

|---|-----|------------------------------------------------------------------|-----|

|   |     | 5.2.4 Complexity Analysis                                        | 93  |

|   | 5.3 | Test Generation using Concolic Testing                           | 94  |

|   |     | 5.3.1 Overview                                                   | 94  |

|   |     | 5.3.2 Selection of Alternate Branches in CFG                     | 95  |

|   | 5.4 | Experiments                                                      | 96  |

|   |     | 5.4.1 Experimental Setup                                         | 96  |

|   |     | 5.4.2 Benchmarks and Assertions                                  | 97  |

|   |     | 5.4.3 Test Generation Results                                    | 97  |

|   | 5.5 | Summary                                                          | 99  |

| 6 | TES | T GENERATION FOR VALIDATION OF CACHE COHERENCE PROTOCOLS         | 100 |

|   | 6.1 | Background                                                       | 101 |

|   | 6.2 | Test Generation for Validation of Cache Coherence Protocols      | 102 |

|   | 6.3 | Scalable Test Generation using Quotient Space                    | 103 |

|   | 6.4 | Experiments                                                      | 109 |

|   |     | 6.4.1 Experimental Setup                                         | 109 |

|   |     | 6.4.2 Test Generation for Quotient Protocol                      | 112 |

|   | 6.5 | Summary                                                          | 114 |

| 7 | SCA | LABLE ACTIVATION OF RARE TRIGGERS                                | 115 |

|   | 7.1 | Motivation                                                       | 116 |

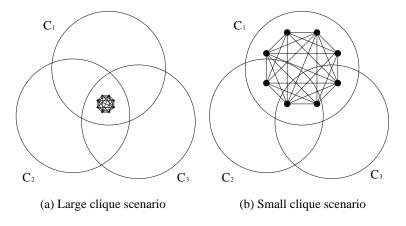

|   |     | 7.1.1 Maximal Clique Problem                                     | 118 |

|   | 7.2 | Scalable Activation of Rare Triggers                             | 120 |

|   |     | 7.2.1 Definition and Notations                                   | 120 |

|   |     | 7.2.2 Mapping Trigger Activation to Clique Cover Problem         | 122 |

|   |     | 7.2.3 Directed Test Generation Scheme                            | 123 |

|   |     | 7.2.4 Test Generation Algorithms                                 | 125 |

|   |     | 7.2.4.1 Test Generation using Clique Enumeration                 | 125 |

|   |     | 7.2.4.2 Efficient Test Generation using Clique Sampling and Lazy |     |

|   |     | Construction                                                     | 127 |

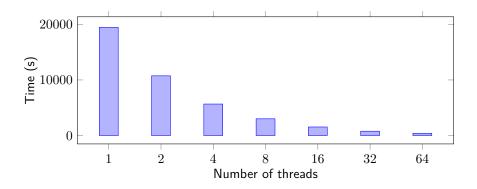

|   |     | 7.2.5 Scalable TRAMAC by Parallelization of Clique Sampling      | 128 |

|   |     | 7.2.6 Effectiveness of Random Clique Sampling                    | 129 |

|   | 7.3 | Experiments                                                      | 132 |

|   |     | 7.3.1 Experimental Setup                                         | 132 |

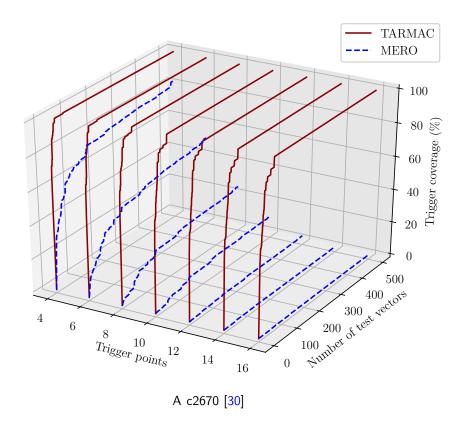

|   |     | 7.3.2 The Effects of Trigger Points                              | 133 |

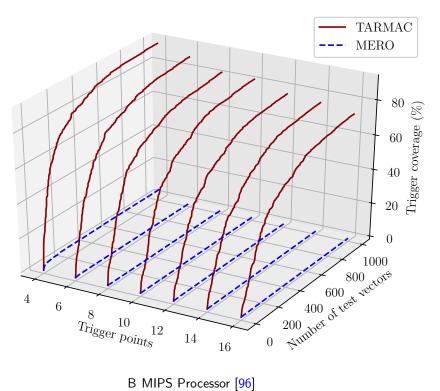

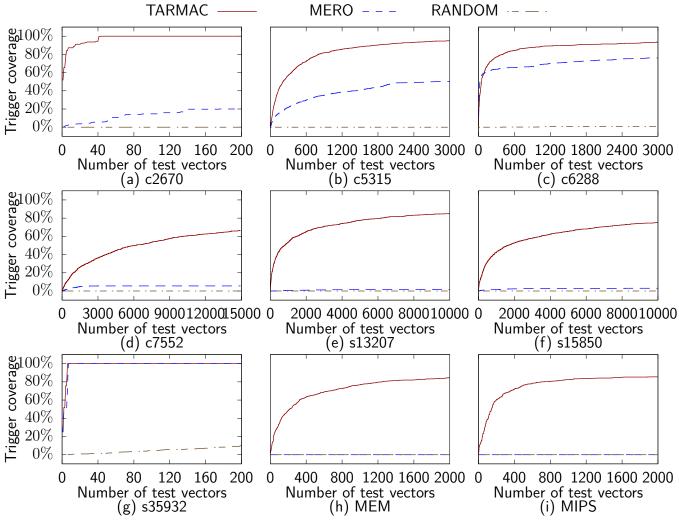

|   |     | 7.3.3 Performance Evaluation                                     | 134 |

|   |     | 7.3.4 Parallelism Evaluation                                     | 138 |

|   |     | 7.3.5 Compactness and Efficiency                                 | 139 |

|   |     | 7.3.6 Trigger Coverage                                           | 141 |

|   | 7.4 | Summary                                                          | 143 |

| 8    | TRO   | JAN DETECTION USING CURRENT-BASED SIDE-CHANNEL ANALYSIS                                                        | 145   |

|------|-------|----------------------------------------------------------------------------------------------------------------|-------|

|      | 8.1   | Problem Formulation and Motivation                                                                             | 146   |

|      |       | 8.1.1 Problem Formulation                                                                                      | 146   |

|      |       | 8.1.2 An Illustrative Example                                                                                  | 147   |

|      |       | 8.1.3 Motivation and Research Challenges                                                                       | 148   |

|      | 8.2   | Generation of Effective Test Patterns                                                                          | 149   |

|      |       | 8.2.1 Generation of the First Patterns                                                                         | 150   |

|      |       |                                                                                                                | 151   |

|      |       |                                                                                                                | 153   |

|      |       | 8.2.2.2 Fitness Computation                                                                                    | 154   |

|      |       | 8.2.2.3 Selection                                                                                              | 154   |

|      |       | 8.2.2.4 Crossover and Mutation                                                                                 | 154   |

|      |       |                                                                                                                | 155   |

|      | 8.3   |                                                                                                                | 156   |

|      |       | $\cdot$                                                                                                        | 156   |

|      |       |                                                                                                                | 157   |

|      |       | taran da antara da a | 158   |

|      |       |                                                                                                                | 160   |

|      |       |                                                                                                                | 162   |

|      |       | · · · · · · · · · · · · · · · · · · ·                                                                          | 163   |

|      |       |                                                                                                                | 163   |

|      |       |                                                                                                                | 166   |

|      | 8.4   |                                                                                                                | 167   |

| 0    | TDA   |                                                                                                                | 1.00  |

| 9    | TRU   | JAN DETECTION USING DELAY-BASED SIDE-CHANNEL ANALYSIS                                                          | 168   |

|      | 9.1   | Test Generation for Path Delay Analysis                                                                        | 169   |

|      |       | 9.1.1 Test Generation for Path Delay Maximization                                                              | 170   |

|      |       | 9.1.2 Hamming-distance based Reordering                                                                        | 172   |

|      | 9.2   | Experimental Results                                                                                           | 174   |

|      |       | 9.2.1 Experimental Setup                                                                                       | 174   |

|      |       | 9.2.2 Path Delay Computation                                                                                   | 175   |

|      |       | 9.2.3 Evaluation Criteria                                                                                      | 176   |

|      |       | 9.2.4 Statistical Evaluation                                                                                   | 176   |

|      | 9.3   | Summary                                                                                                        | 180   |

| 10   | CON   | CLUSIONS AND FUTURE WORK                                                                                       | 181   |

|      | 10 1  | Conclusions                                                                                                    | 181   |

|      |       |                                                                                                                | 184   |

|      |       |                                                                                                                |       |

| APPE | ENDIX | X: LIST OF PUBLICATIONS                                                                                        | 186   |

| REFE | REN   | CES                                                                                                            | 188   |

| DIOC | DADI  | HICAL SKETCH                                                                                                   | 1 / 0 |

# LIST OF TABLES

| Table | e_<br>_                                                                                                                               | page |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|------|

| 1-1   | Seven classes of SoC security vulnerabilities                                                                                         | 20   |

| 3-1   | Commonly used temporal operators in LTL [1]                                                                                           | 43   |

| 3-2   | Types of vulnerabilities explored in the six benchmarks                                                                               | 50   |

| 4-1   | The results of satisfiability checking in line 10 of Algorithm 1 for the target BB7                                                   | 67   |

| 4-2   | Comparison of target coverage using [2], [3] and our approach on 20 targets                                                           | 79   |

| 4-3   | Comparison of memory requirement using EBMC and our approach on one target                                                            | 81   |

| 4-4   | The number of iterations that each block is selected as the best alternative block in exploring paths for Listing 4.1                 | 84   |

| 5-1   | Performance comparison of our approach with EBMC [4] in activating assertions                                                         | 98   |

| 6-1   | Gem5 simulation parameters                                                                                                            | 110  |

| 7-1   | Comparison of TARMAC with random simulation and MERO for trigger activation coverage over 1000 randomly sampled 8-trigger conditions. | 136  |

| 7-2   | Comparison of TARMAC with random simulation and MERO for trigger activation coverage over 1000 randomly sampled 8-trigger conditions. | 137  |

| 8-1   | Comparison of MaxSense with NDT+GA [5] and MERS-s [6] over 1000 Trojans                                                               | 159  |

| 9-1   | Performance comparison of our approach with random simulation and ATPG over 1000 randomly sampled Trojans.                            | 178  |

| 9-2   | Test generation time of our approach in all benchmarks                                                                                | 179  |

# LIST OF FIGURES

| Figur | <u>re</u>                                                                                                                                                                | page     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1-1   | Various applications of IoT devices. [7]                                                                                                                                 | 13       |

| 1-2   | An SoC design integrates a wide variety of IPs in a chip                                                                                                                 | 14       |

| 1-3   | Among the recorded vulnerabilities in 2015 from MITRE/NIST CVE website, 43% were software-assisted hardware vulnerabilities. [8] $\dots \dots \dots \dots \dots \dots$ . | 15       |

| 1-4   | The impact of vulnerabilities and the hardness of patching increase from software, firmware to hardware                                                                  | 15       |

| 1-5   | Hardware vulnerabilities come from careless designers and buggy EDA tools in hardware design, and untrusted foundries in manufacturing.                                  | re<br>16 |

| 1-6   | The overview of my research                                                                                                                                              | 17       |

| 1-7   | Four major categories of formal verification methods. [9]                                                                                                                | 18       |

| 1-8   | Simulation-based validation                                                                                                                                              | 18       |

| 1-9   | Side-channel analysis                                                                                                                                                    | 19       |

| 1-10  | Poor observability in hardware validation. [10]                                                                                                                          | 21       |

| 1-11  | Full system FSM of three processor MESI-based system. [11]                                                                                                               | 23       |

| 1-12  | An example hardware Trojan                                                                                                                                               | 24       |

| 1-13  | Random simulation cannot guarantee the coverage of all targets                                                                                                           | 25       |

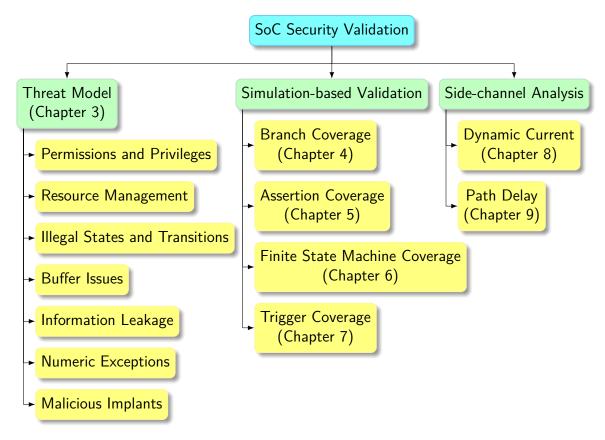

| 1-14  | Dissertation outline                                                                                                                                                     | 29       |

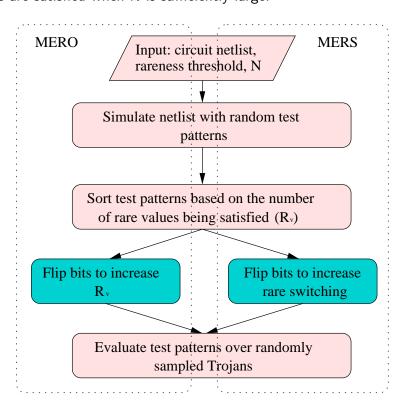

| 2-1   | The frameworks of MERO [12] and MERS [6]                                                                                                                                 | 33       |

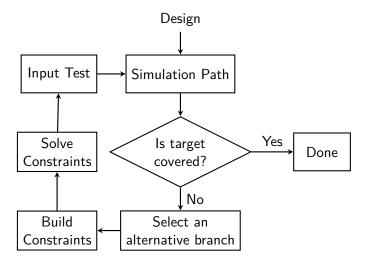

| 2-2   | The main steps of concolic testing.                                                                                                                                      | 34       |

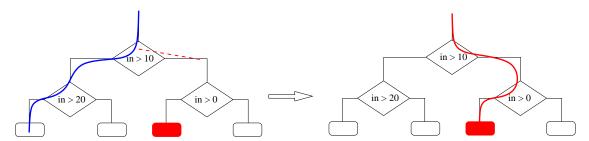

| 2-3   | Alternative branch selection in concolic testing                                                                                                                         | 35       |

| 2-4   | Side-channel analysis detects hardware Trojans by comparing the difference of side channel signatures.                                                                   | 38       |

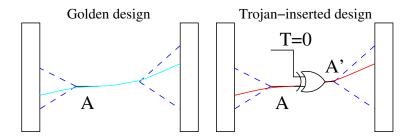

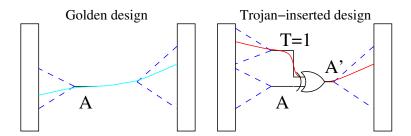

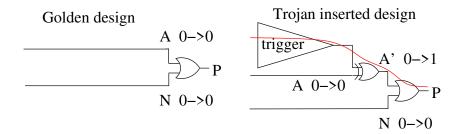

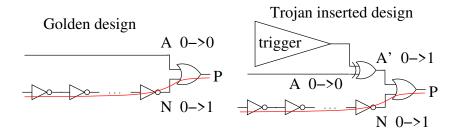

| 2-5   | Two types of impact on path delay from hardware Trojans [13]                                                                                                             | 39       |

| 3-1   | The framework for defining and utilizing SoC security assertions                                                                                                         | 42       |

| 3-2   | Overview of our assertion generation framework for different classes of vulnerabilities                                                                                  | 46       |

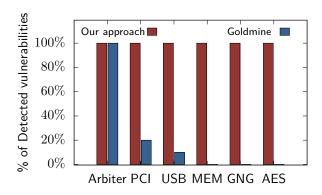

| 3-3   | Comparison of detected vulnerabilities by our assertions and Goldmine [14]                                                                                               | 49       |

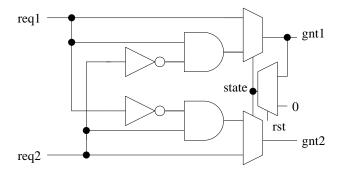

| 3-4   | A simple arbiter with four inputs (clk not shown) and two outputs                                                                                                        | 50       |

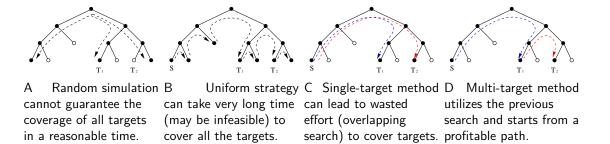

| 4-1 | Comparison of four approaches in covering two targets $T_1$ and $T_2$                                                                                       | 59  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

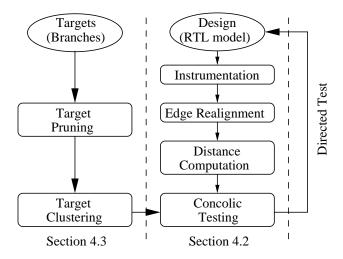

| 4-2 | The overview of our test generation framework using concolic testing                                                                                        | 60  |

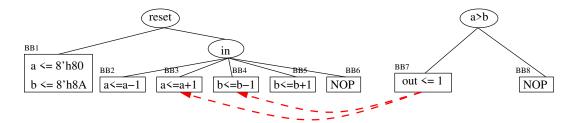

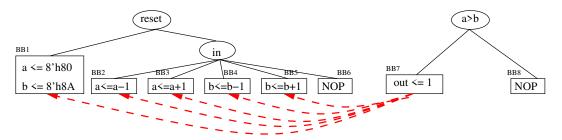

| 4-3 | Comparison of edge realignment by our approach and [3]                                                                                                      | 63  |

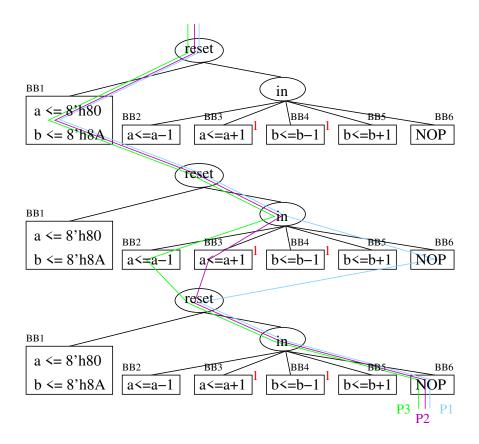

| 4-4 | The distance between a basic block and the target in realigned CFGs                                                                                         | 69  |

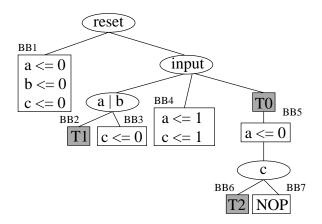

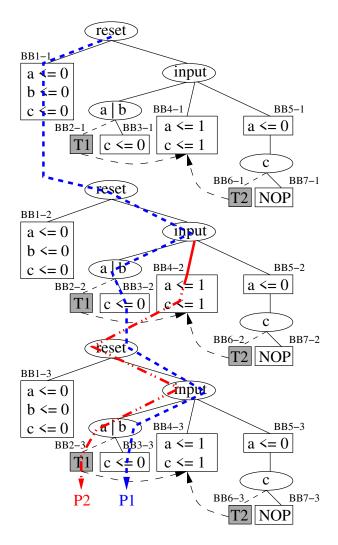

| 4-5 | CFG for the design in Listing 4.2. T0, T1, and T2 represent three targets                                                                                   | 73  |

| 4-6 | Two simulation paths for the design in Listing 4.2 (unrolled for three cycles)                                                                              | 75  |

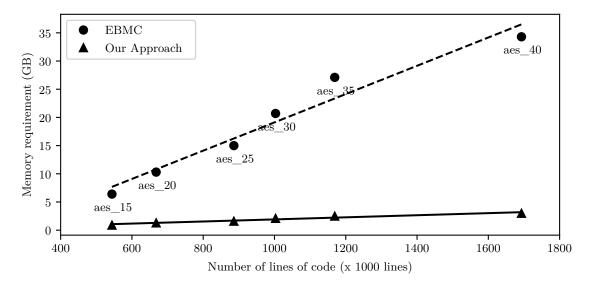

| 4-7 | The comparison of memory requirements of our approach and EBMC                                                                                              | 82  |

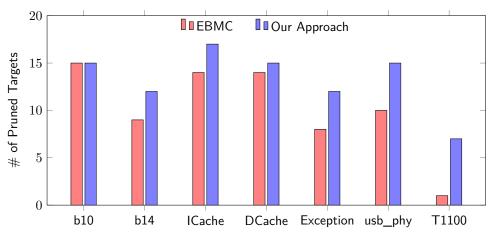

| 4-8 | The number of targets that are pruned                                                                                                                       | 83  |

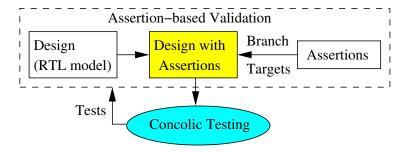

| 5-1 | Our approach converts assertions to branch targets and activates them non-vacuously.                                                                        | 87  |

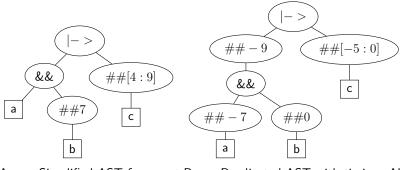

| 5-2 | AST adjustment with timing. Logic operator, implication and delay are non-terminal nodes (oval), and others are terminals (rectangle)                       | 91  |

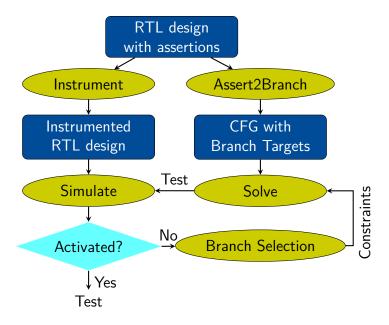

| 5-3 | Overview of our framework to activate the branches converted from assertions                                                                                | 94  |

| 5-4 | Chaining of related blocks in CFGs to assist alternative branch selection                                                                                   | 95  |

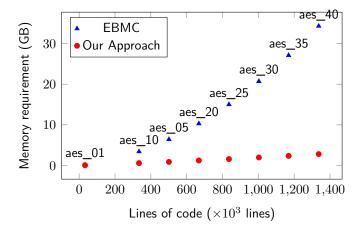

| 5-5 | Memory requirement with respect to the total lines of code in custom benchmarks                                                                             | 99  |

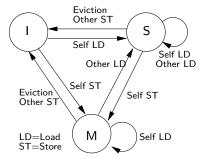

| 6-1 | State transitions for a cache block in MSI protocol                                                                                                         | 101 |

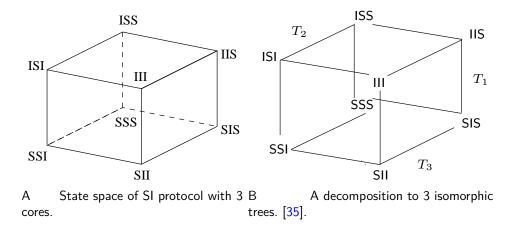

| 6-2 | The decomposition of the state space of SI protocol with 3 cores                                                                                            | 103 |

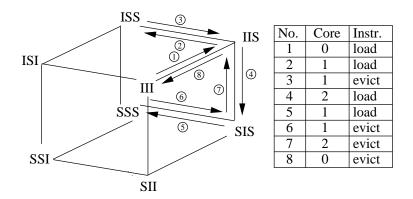

| 6-3 | The tests generated by Euler traversal of the upper right sub-structure of hypercube.                                                                       | 103 |

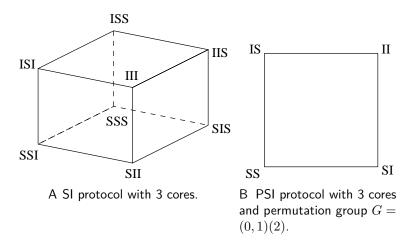

| 6-4 | The original state space and its corresponding quotient space of SI with 3 cores                                                                            | 106 |

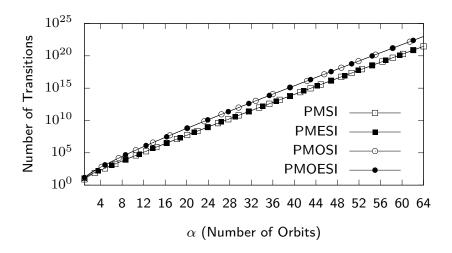

| 6-5 | Complexity of quotient protocol with respect to number of orbits $lpha.$                                                                                    | 107 |

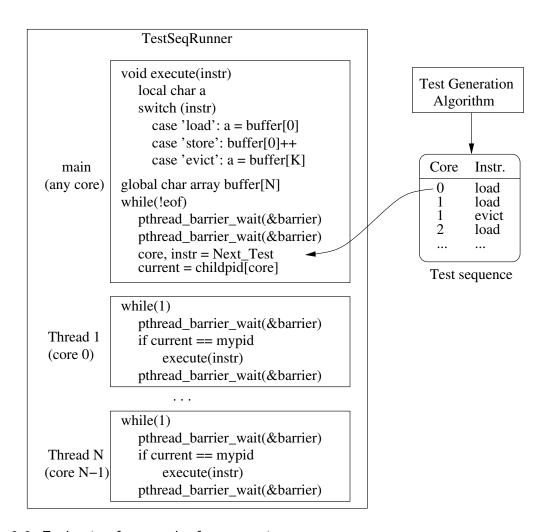

| 6-6 | Evaluation framework of our experiment                                                                                                                      | 111 |

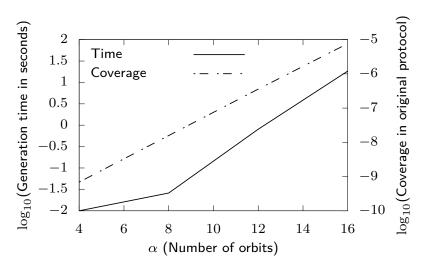

| 6-7 | Test generation time (left y-axis) and coverage (right y-axis) in the original space (MESI with 32 cores) of PMESI protocol with different number of orbits | 112 |

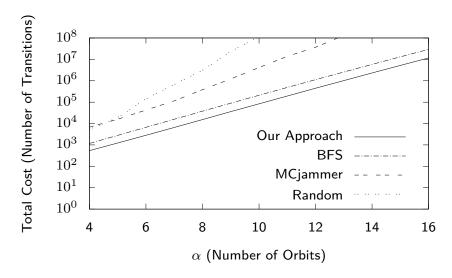

| 6-8 | Total cost vs. number of orbits ( $lpha$ ) for PMESI protocol with 64 cores                                                                                 | 113 |

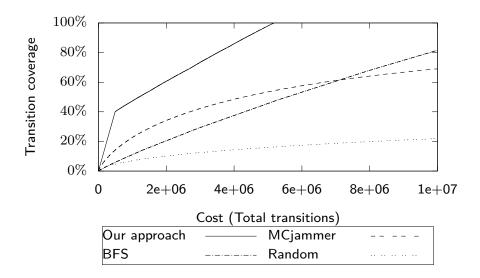

| 6-9 | Transition coverage vs. time cost for PMESI protocol with 64 cores and 15 orbits                                                                            | 114 |

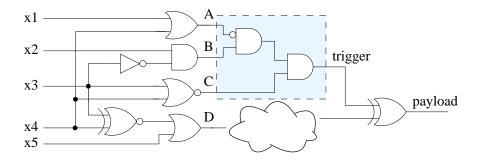

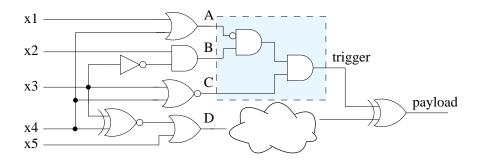

| 7-1 | A simple combinational Trojan with 3 triggers                                                                                                               | 116 |

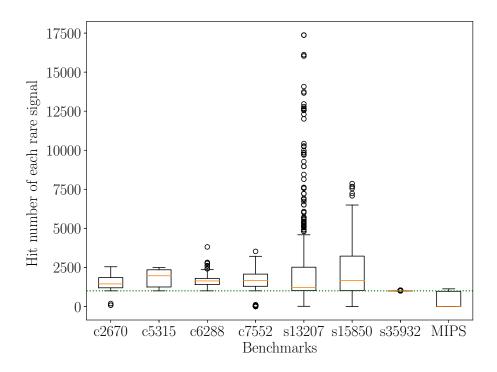

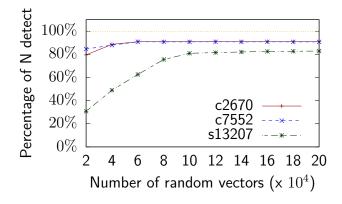

| 7-2 | The number of times each rare signal is activated by by MERO                                                                                                | 119 |

| 7-3 | The percentage of rare signals that are activated at least $N$ times by MERO                                                                                | 119 |

| 7-4 | Overview of our proposed (TARMAC) paradigm                                                                                                                  | 120 |

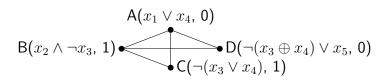

| 7-5  | A hardware Trojan with a trigger condition constructed by three rare signals                                                                | 121      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 7-6  | The satisfiability graph with 4 $PTS$ (A,B,C,D) from Figure 7-5, with logic expressions and rare values in parentheses.                     | s<br>122 |

| 7-7  | The relative size of trigger conditions compared to maximal SAT cliques                                                                     | 131      |

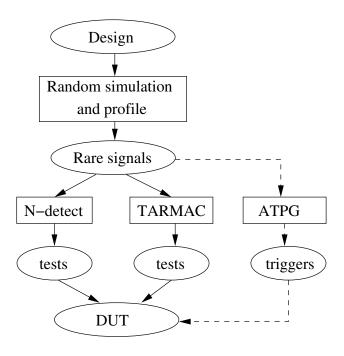

| 7-8  | Experimental setup for evaluation of TARMAC compared to $N{\rm -detect}$ approach                                                           | 133      |

| 7-9  | Trigger condition coverage of TARMAC and MERO on c2670 and MIPS with respect to the number of test vectors and the number of trigger points | 135      |

| 7-10 | The time of Algorithm 8 applied in MIPS with different number of threads                                                                    | 139      |

| 7-11 | Trigger coverage with respect to the number of test vectors                                                                                 | 140      |

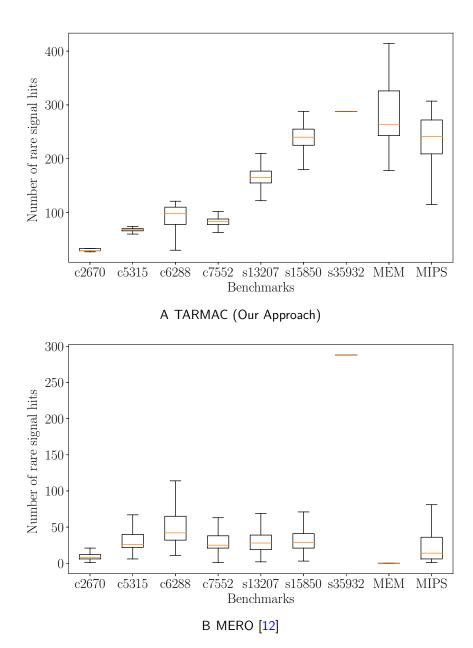

| 7-12 | The distribution of rare signal hits by the generated test set in all benchmarks                                                            | 142      |

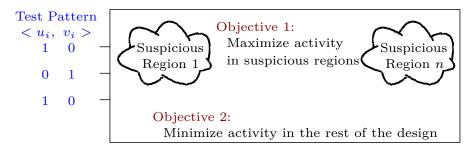

| 8-1  | The two objectives to maximize the sensitivity in current-based side-channel analysis.                                                      | 146      |

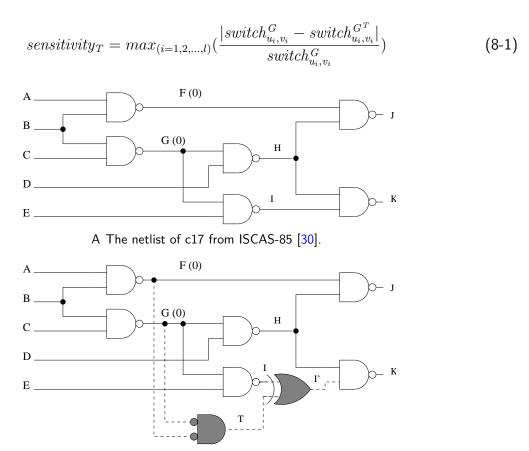

| 8-2  | The example of a Trojan inserted into c17                                                                                                   | 147      |

| 8-3  | The overview of our framework MaxSense                                                                                                      | 149      |

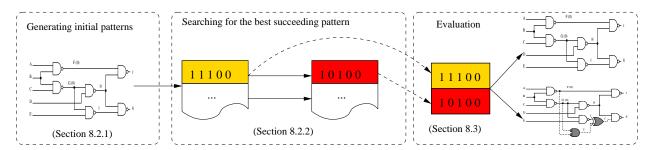

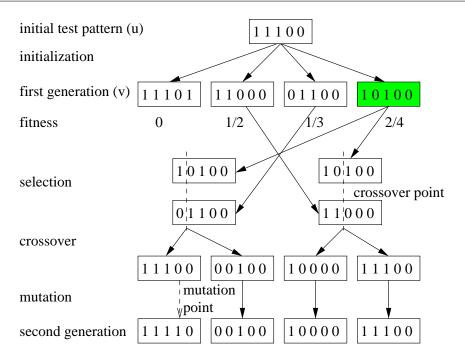

| 8-4  | The first iteration of GA for generating the best second pattern for $u=11100.\ .\ .\ .$                                                    | 153      |

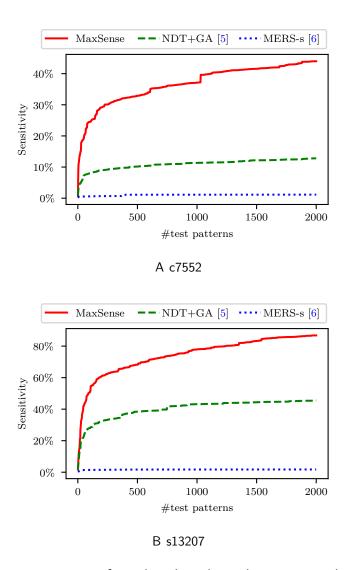

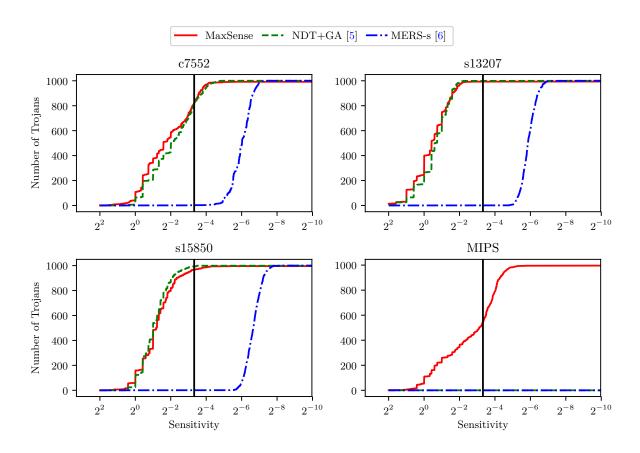

| 8-5  | The average sensitivity of two benchmarks with respect to the length of tests                                                               | 161      |

| 8-6  | The distributions of sensitivities by three approaches over 1000 Trojans                                                                    | 162      |

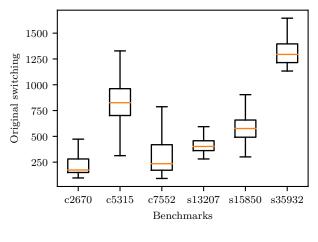

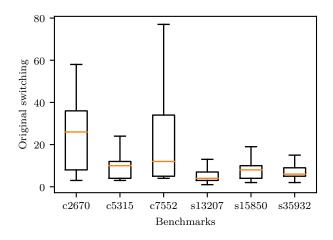

| 8-7  | The distribution of the original switching in the golden design                                                                             | 164      |

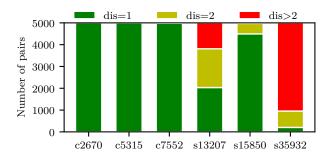

| 8-8  | Hamming distance of all pairs of test patterns by MaxSense                                                                                  | 165      |

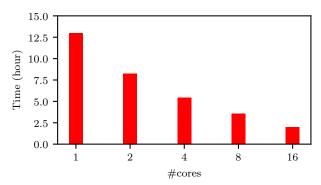

| 8-9  | The test generation time of MaxSense with multi-core platforms for MIPS processor.                                                          | 166      |

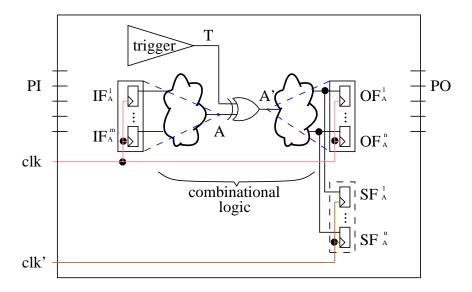

| 9-1  | Path delay measurement using shadow registers [15]                                                                                          | 169      |

| 9-2  | The small delay difference by existing approaches with the same critical path                                                               | 171      |

| 9-3  | Our approach maximizes delay difference by changing critical paths                                                                          | 171      |

| 9-4  | The constraints to ensure a critical path from the trigger to the output layer                                                              | 173      |

| 9-5  | A longer path may mask the delay from the Trojan.                                                                                           | 174      |

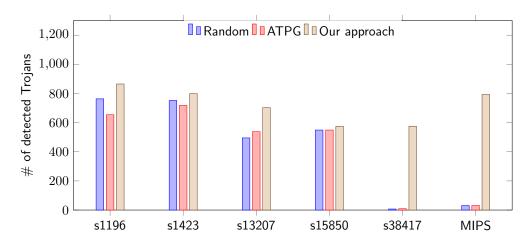

| 9-6  | The number of detected Trojan given the noise of $\pm 7.5\%$ noise                                                                          | 177      |

Abstract of Dissertation Presented to the Graduate School of the University of Florida in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

#### TEST GENERATION FOR SYSTEM-ON-CHIP SECURITY VALIDATION

By

Yangdi Lyu

May 2020

Chair: Prabhat Mishra Major: Computer Science

Hardware security validation is crucial to ensure the integrity of System-on-Chip (SoC) designs. Attackers take advantage of SoC security vulnerabilities to inject malicious functionality into the design. Validation of SoC security is challenging due to increasing SoC complexity coupled with utilization of a wide variety of third-party components from potentially untrusted suppliers. There are two major problems in SoC security validation. While there is extensive research in defining software-level vulnerabilities, there is very limited effort in classifying the potential SoC security vulnerabilities. Moreover, there is a lack of efficient techniques for simulation-based security validation as well as side-channel analysis.

In this dissertation, I propose efficient test generation techniques for SoC security validation. I have classified SoC security validations into seven major categories, and proposed an assertion-based approach to address these validations. To activate these security assertions, I have developed a scalable test generation framework interleaving concrete simulation and symbolic execution. I have shown that clique cover can be utilized to develop efficient tests to detect malicious implants (hardware Trojans). I have also developed an efficient test generation technique to detect hardware Trojans using current-based as well as delay-based side-channel analysis. Experimental results demonstrate that the proposed test generation techniques are effective in validation of SoC security validations and side-channel analysis.

12

# CHAPTER 1 INTRODUCTION

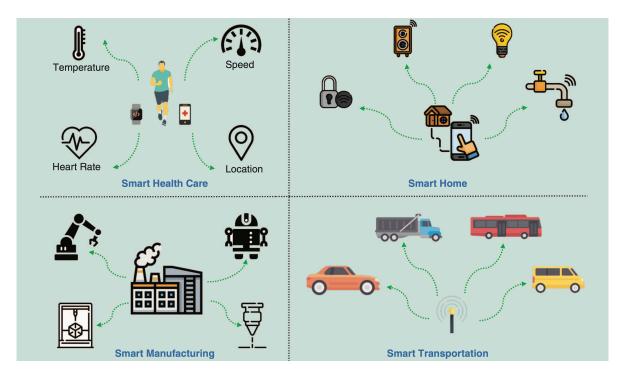

We are living in a connected world where a wide variety of computing and sensing components interact with each other. Reliability, safety and privacy are essential in the fabric of Internet-of-Things (IoT) as intelligent computing devices are increasingly embedded in every possible device in our daily life such as wearable devices (e.g., fitness trackers, smart watches, and medical devices), autonomous vehicles and smart homes, as shown in Figure 1-1. Many of these devices collect real-time data using sensors, and share data with other devices or the cloud without human intervention. Any failure of security and trust requirements of IoT devices may cause severe damages to critical infrastructure, endangering human life, or violating personal privacy. Since IoT devices are connecting to each other as well as communicating to the cloud to provide the required services, even one vulnerable edge device can expose the whole cluster to potential attacks. IoT applications also bring important considerations such as long application life and dynamic use-case scenarios. These IoT devices are making the world smarter, but raising the concern of security and privacy of human life.

Figure 1-1. Various applications of IoT devices. [7]

System-on-Chip (SoC) is the brain behind the computing devices today. Unlike micro-controller based designs in the past, even resource constrained IoT devices nowadays incorporate one or more complex SoCs. A typical SoC consists of multiple Intellectual Property (IP) cores including processor, memory, controllers, converters, debug infrastructure, etc. As shown in Figure 1-2, a typical IoT device collects data from various types of sensors, converts the data using an analog-to-digital converter (ADC), and shares the computed results to the clouds through different forms of network protocols.

Figure 1-2. An SoC design integrates a wide variety of IPs in a chip.

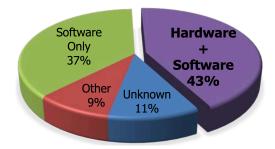

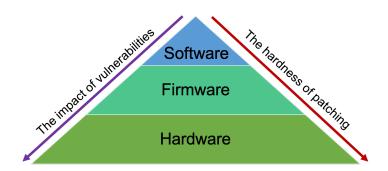

The risk of attacks on IoT devices has increased more than anytime before. The attackers can explore a wide variety of vulnerabilities on these devices to mount attacks in different levels, such as hardware level, firmware level, and software level. Based on the data from MITRE/NIST Common Vulnerability Exposure (CVE) website, 43% of all vulnerabilities in 2015 were software-assisted hardware vulnerabilities [8], as shown in Figure 1-3. Among the vulnerabilities from different levels, the vulnerabilities from hardware level are the most dangerous for two reasons as shown in Figure 1-4.

1. Significant Impact: Hardware vulnerabilities allow attackers to mount attacks to a wide variety of IoT devices using the same hardware design. Tools such as anti-virus are not viable to protect from these attacks as these vulnerabilities are in the level of hardware. For example, Spectre [16] and Meltdown [17] explore the out-of-order execution and speculative execution in modern processors to steal information across isolated applications. These two attacks are shown to be successful in a lot of desktops, laptops, cloud servers, as well as smartphones.

Difficult to Fix: In contrast to a software vulnerability which can be modified after deployment, fixing a hardware vulnerability becomes significantly difficult and expensive. Existing approaches try to mask some of the vulnerabilities using firmware patching or utilizing in-built reconfigurable primitives. However, these approaches may not work in all scenarios.

Due to these two reasons, an attack that explores hardware vulnerabilities can be successfully repeated on every instance of IoT devices using the same vulnerable hardware.

Figure 1-3. Among the recorded vulnerabilities in 2015 from MITRE/NIST CVE website, 43% were software-assisted hardware vulnerabilities. [8]

Figure 1-4. The impact of vulnerabilities and the hardness of patching increase from software, firmware to hardware.

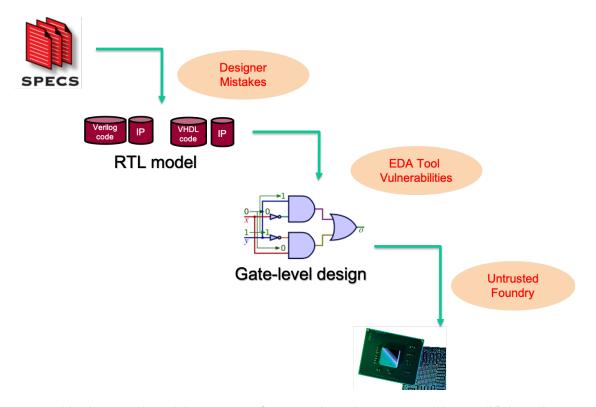

Hardware vulnerabilities may come from three main sources. (i) As the design process contains many steps, starting from specification, synthesis, integration, to manufacturing, there are a lot of parties and tools involved. Errors and vulnerabilities can be introduced by careless designers and buggy electronic design automation (EDA) tools, as shown in the upper part of Figure 1-5. (ii) Drastic increase in SoC complexity has led to popularity in IP-based design approach. SoC design companies tend to outsource IPs to third parties to meet aggressive time-to-market constraints and reduce design cost. The vulnerabilities may be introduced by

these pre-verified hardware IPs from untrusted third-party vendors as well as the untrusted manufacturers, as shown in the lower part of Figure 1-5. (iii) The running environments of these devices are heterogeneous and possibly connected and unprotected. Vulnerabilities in one device may open a backdoor in other devices. SoC validation tries to ensure that the integrated design is free of vulnerabilities and meets all constraints including area, power, and timing overhead.

Figure 1-5. Hardware vulnerabilities come from careless designers and buggy EDA tools in hardware design, and untrusted foundries in manufacturing.

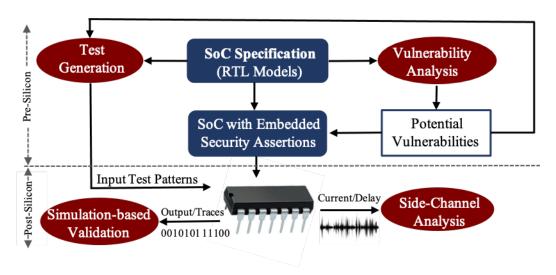

In this dissertation, I develop approaches for both simulation-based validation and side-channel analysis to detect hardware security vulnerabilities. Specifically, the focus of this dissertation is to generate high quality tests to achieve high validation coverage as well as maximize the side-channel anomaly, as shown in Figure 1-6. First, I develop a taxonomy of SoC security vulnerabilities and generate assertions for each of them. Second, I develop a test generation framework to activate all the assertions by converting assertions into equivalent branches and generating tests to activate the branches using concolic testing. Third,

I develop test generation approaches for both simulation-based validation and side-channel analysis to detect hardware Trojans. The proposed test generation framework combines advantages of both logic testing and side-channel analysis to improve the side-channel sensitivity. The rest of this chapter is organized as follows. Section 1.1 introduces existing hardware validation techniques. Section 1.2 outlines the hardware security validation challenges in SoCs. Section 1.3 summarizes the contributions of this dissertation. Finally, Section 1.4 describes the structure of this dissertation.

Figure 1-6. The overview of my research.

#### 1.1 SoC Validation Methods

Validation is widely acknowledged as a major bottleneck in today's SoC design methodology. Various studies suggest that validation and verification consume about 70% of the overall SoC design effort (cost and time) [18]. There are three broad categories of SoC validation techniques: formal verification, simulation-based validation, and side-channel analysis.

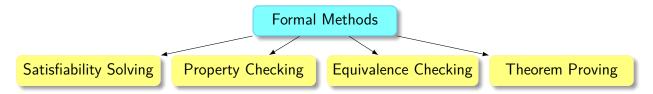

#### 1.1.1 Formal Methods

There are various types of formal methods in SoC validation, such as satisfiability (SAT) solving, property (model) checking, equivalence checking, and theorem proving [9], as shown in Figure 1-7. The goal of formal methods is to provide mathematical guarantees about the

correctness of a design. For example, property checking converts the design into mathematical representation, and formally proves the correctness of the design with respective to specific properties. A major challenge in formal methods is that it needs to covert the design into a specific formal language, which is can be error-prone. Most importantly, formal methods face the state explosion problem for large designs.

Figure 1-7. Four major categories of formal verification methods. [9]

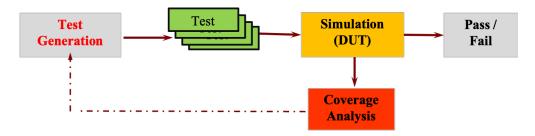

#### 1.1.2 Simulation-based Validation

Simulation-based validation applies tests to the design and checks the functional outputs, as shown in Figure 1-8. It is widely used for functional validation to cover various features such as all statements, all branches, etc. The quality of tests are critical to achieve high (or complete) coverage of functional scenarios. While simulation using random and constrained-random tests is scalable, it cannot guarantee full coverage of all functional scenarios. Directed test generation approaches have been proposed to generate high quality tests to achieve high coverage for simulation-based validation [19].

Figure 1-8. Simulation-based validation.

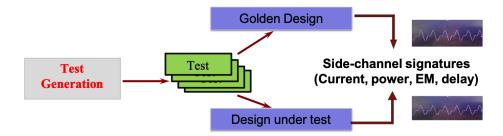

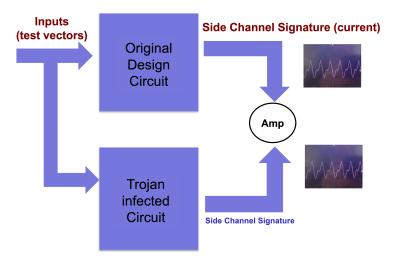

#### 1.1.3 Side-channel Analysis

In contrast to simulation-based validation which relies on the functional outputs of a design, side-channel analysis compares side-channel signatures, such as power, current, electromagnetic radiation, path delay, etc., as shown in Figure 1-9. When the side-channel difference between the golden design and the design-under-test (DUT) exceeds a threshold, the DUT is likely to be different from the golden design. The threshold exists due to the variation introduced by the manufacturing process and the noise from the measurement environment. Therefore, if the applied tests is not able to generate a large difference in side-channel signatures (higher than the threshold), side-channel analysis will fail to give any conclusion regarding the DUT.

Figure 1-9. Side-channel analysis.

In this dissertation, I mainly focus on simulation-based validation and side-channel analysis. In particular, I develop novel tools and techniques to improve coverage in simulation-based validation as well as signature difference in side-channel analysis.

# 1.2 SoC Security Validation Challenges

There are some similarities as well as differences between SoC functional validation and SoC security validation. Some functional validation techniques can be used to detect security vulnerabilities. For example, branch coverage in functional validation can help to find hardware Trojans when they are hidden inside rare branches. Similarly, finite state machine coverage in functional validation can also help find hardware Trojans since hardware Trojans are likely to change certain states and transitions when they are triggered. However, there is one fundamental difference that introduces significant challenge to SoC security validation, i.e., the unknown nature of these vulnerabilities. Unlike functional validation where the coverage goal is well defined, security vulnerabilities are typically unknown. This section describes the major challenges in SoC security validation.

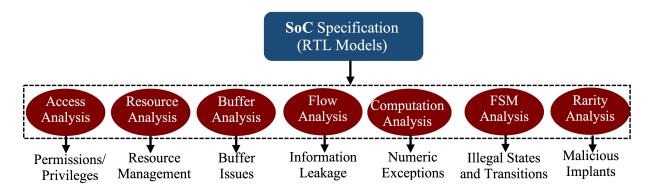

#### 1.2.1 A Wide Variety of Vulnerabilities

While there is extensive research in defining software-level vulnerabilities, there is very limited effort in developing a comprehensive classification of potential SoC vulnerabilities. A lot of work has been done in the area of hardware Trojans, but it only represents a small fraction of the SoC vulnerability space. Specifically, it belongs to one of the many classes of vulnerabilities that I have summarized after reviewing a wide variety of security vulnerabilities listed in the National Vulnerability Database [20]. Table 1-1 shows the seven types of vulnerabilities that will be discussed in Chapter 3 in detail. As listed in Table 1-1, the vulnerabilities in SoC are so diverse that great validation efforts are needed to analyze, detect and remove all of them.

Table 1-1. Seven classes of SoC security vulnerabilities

| Vulnerability                  | Example                                                 |

|--------------------------------|---------------------------------------------------------|

| Permissions and Privileges     | Insufficient privilege/access checking                  |

| Resource Management            | Illegal access to resources, misuse of design-for-debug |

|                                | infrastructures                                         |

| Illegal States and Transitions | Illegal states and transitions, backdoor of undefined   |

|                                | states/transitions                                      |

| Buffer Issues                  | Unexpected behavior of heterogeneous buffers            |

| Information Leakage            | Information leaks from secure world to non-secure world |

| Numeric Exceptions             | Erroneous/illegal behaviors (e.g., divide by zero)      |

| Malicious Implants             | Hardware Trojans, inserted by untrusted third party     |

#### 1.2.2 Controllability and Observability

One challenge in hardware validation is the low controllability and observability of internal signals. Controllability represents the ability to control any internal signal, which requires the debug engineers to generate the correct stimulus for primary inputs. For example, it is hard to activate the trigger signal of a hardware Trojan whose trigger condition is extremely rare. Observability for validation represents the ability to reveal the internal bugs, which is also hard since the internal bugs may be hidden before it reaches the primary outputs or other observable structures, as shown in Figure 1-10. Even with the help of Design-for-Debug (DfD) architecture, the visibility is very limited for internal signals (e.g., 256 signals can be traced

Figure 1-10. Poor observability in hardware validation. [10]

for 2048 cycles in a multi-million gate design) during post-silicon execution. Assertion-based validation is a common practice in industry for functional validation. The embedded assertions can catch any unexpected behavior which increases the observability of internal activities inside the design. For example, an assertion can check that the output of an adder is equal to the sum of its inputs whose implementation may be different in different designs. Any bug in the design that violates the predefined properties in assertions can be easily detected. The observability of internal states enables faster localization of errors, which reduces the overall validation time significantly. Although assertions have been successful in functional validation, it is not clear if non-functional behaviors (e.g., security) can be posed as constraints (assertions). For example, security validation needs to check the vulnerability of potential information leakage. However, there are no easy constraints to ensure that there is no path to leak information from secure world to unsecure world.

# 1.2.3 Lack of Effective and Scalable Validation Techniques

Similar to functional validation, security vulnerabilities can also be detected using simulation-based approaches and side-channel analysis. Simulation using random and constrained-random tests is widely used in traditional validation methodology. Unfortunately,

even billions or trillions of constrained-random tests cannot cover many complex and corner-case scenarios in today's industrial designs. Another problem in random and constrained-random tests is the slow speed of simulation. With billions or trillions of tests, it is expected to take months to finish simulation. Directed tests are promising as they can achieve comparable coverage with significantly less tests. Directed testing is also promising in covering specific cases that are not covered by random or constrained-random tests. In contrast to simulation-based approaches which focus on the functionality of the design, side-channel analysis checks if a vulnerability exists by comparing the side-channel signatures from the golden design and the design-under-test. However, the sensitivity of side-channel analysis achieved by state-of-the-art approaches is too small to detect vulnerabilities under current process variations and environmental noise.

There are promising formal approaches to solve specific problems related to hardware security vulnerabilities, such as equivalence checking in arithmetic circuit to detect hardware Trojans [9], and bounded model checking for activating security assertions. However, these approaches are not effective and scalable to detect a wide variety of vulnerabilities in SoC security validation due to three fundamental challenges: increasing complexity of finite state machines, stealthy nature of security vulnerabilities, and exponential validation space. The remainder of this section describes these challenges in detail.

Complex Finite State Machines: For the ease of illustration, I use cache coherence protocol as an example to explain why complex finite state machine is a challenge for SoC security validation. System designers incorporate multi-core processors to meet the increasing performance requirements. To address the memory bottleneck, caching has been the most effective approach to reduce the memory access time for several decades. When the same data is cached by different processors, cache coherence protocols are employed to guarantee that a read always returns most recently written data. This rule requires the whole system to monitor every copy of the same data across multiple processors. To boost the overall performance and reduce the number of flushing and loading, the design of cache coherence protocols is

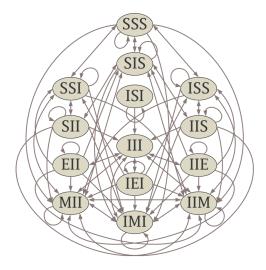

also becoming more and more complex, from the simplest MSI to MESI and MOSI, then to MOESI [21] and MESIF [22]. With the increasing number of cores and complexity of cache coherence protocols, the compound state and transition space is getting exponentially complex. The first complexity comes from the exponentially growing number of states and transitions. For example, in 8-core and 16-core MESI protocols, there are 5 thousands and 2.6 million transitions, respectively. It is infeasible to generate tests and traverse every state with more cores. The second complexity comes from the obscure structures. Although the FSM of each cache controller is easy to understand, the product finite state machine for modern cache coherence protocols is quite obscure. For example, Figure 1-11 shows the obscure finite state machine of a MESI protocol with only three cores. With more cores, the structure of the FSM is expected to be too obscure to apply any analysis.

Figure 1-11. Full system FSM of three processor MESI-based system. [11]

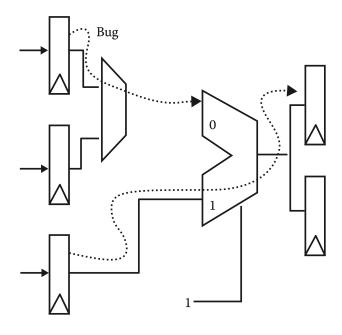

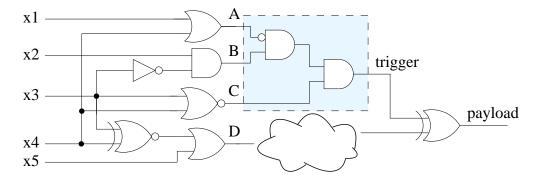

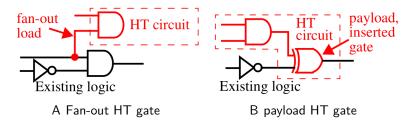

**Stealthy Nature of Vulnerabilities:** To illustrate the stealthy nature of vulnerabilities, I use malicious implants as an example. Hardware Trojans [23, 24] are malicious modifications incorporated during the System-on-Chip (SoC) design cycle [23, 25–28]. As IC design and fabrication process becomes more and more globalized, the threat of hardware Trojan attacks is increasing due to potential malicious modifications at different stages of the design and fabrication process [25, 29]. A Trojan normally consists of a rare trigger condition and a

payload, as shown in Figure 7-1. Trigger condition is carefully crafted such that it is only activated under extremely rare conditions, and the functionality of a design remains exactly the same as the golden design under most of the running cases. The inherent stealth of trigger condition makes hardware Trojan detection a challenging problem. The number of choices to construct trigger conditions grow exponentially with the complexity of SoCs. For example, even for a small ISCAS benchmark (c880 with only 451 gates) [30], there are approximately  $10^{11}$  triggers possible with only four trigger points. The number would be exponentially higher if we consider triggers with different number of trigger points. Clearly, it is infeasible to generate and apply so many directed tests to activate Trojan triggers even for a tiny benchmark.

Figure 1-12. An example hardware Trojan.

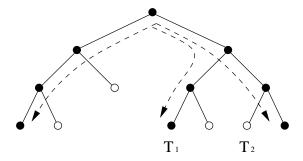

**Exponential Validation Space:** As the complexity of SoC designs grows exponentially, the validation efforts also grow exponentially to achieve reasonable coverage analysis. Millions of random or constrained-random tests are able to quickly cover majority of functional scenarios (targets). However, it is not always possible to cover all scenarios using these tests and the number of remaining targets can be huge (hundreds or thousands) in case of today's industrial designs. For specific targets, random simulation cannot guarantee to detect them within debug budgets. For example, Figure 1-13 shows the scenario that three random simulation paths can cover the target  $T_1$  but cannot cover the target  $T_2$ . Verification engineers usually manually write test cases to cover the remaining hard-to-activate scenarios. Due to the increasing design complexity, the number of remaining hard-to-activate scenarios can be exponential. While such manual test case development is possible for small designs, it would be

infeasible to develop directed test for large designs. Coming up with manual test cases can be both error-prone and time-consuming due to many trial-and-error iterations.

Figure 1-13. Random simulation cannot guarantee the coverage of all targets.

Automated test generation is necessary to achieve full coverage of all remaining targets that are not covered by random simulation. There has been extensive research in test generation for code coverage in RTL models using formal methods [31, 32]. Although formal methods can cover specific scenarios directly, they require tedious and error-prone translation from real design to their own languages and suffer from state explosion for large designs. Semi-formal approach, such as concolic testing, is promising to address the scalability problem by combining the advantages of random simulation and formal methods to activate targets efficiently. The idea of concolic testing comes from software testing domain [33, 34]. It uses depth-first-search (DFS) or breadth-first-search (BFS) to quickly find input patterns to activate specific bugs in software. However, none of these search strategies can work for large programs due to path explosion problem.

#### 1.3 Research Contributions

Directed test generation is a promising and efficient method for hardware security validation. Compared to random simulations, directed test generation can reach a specific goal with a drastically small number of tests. This dissertation mainly focuses on directed test generation for validation of hardware security. Specifically, it makes the following fundamental contributions: (1) the taxonomy of SoC security vulnerabilities, (2) simulation-based validation by exploring the specification, structures and functionality, and (3) side-channel analysis based

on dynamic current and path delay to detect malicious implants (hardware Trojans). The reminder of this section outlines these contributions.

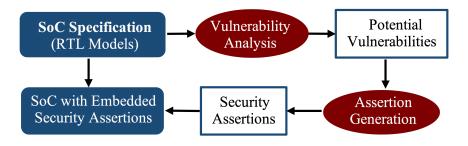

Taxonomy of Security Vulnerabilities: Existing SoC validation techniques mainly focus on the functional behaviors defined in the specification. Traditionally, SoC security vulnerabilities are not considered as expected functional behaviors. For example, an unspecified transition in finite state machine (FSM) is one of the main sources of security vulnerabilities. While assertion-based validation (ABV) is the de facto standard for functional validation, there are no prior efforts to define and monitor SoC security vulnerabilities. Given the importance of SoC security, I classify security vulnerabilities into seven categories, and propose a framework for defining and utilizing SoC security assertions to detect each category of vulnerabilities.

Code Coverage for Multiple Targets: Concolic testing is promising to cover the rare scenarios that are not covered by millions of random tests. It addresses the state explosion problem in formal methods. However, existing concolic testing approaches in RTL model are not effective in path selection and not scalable due to overlapping search. To address these two problems, an efficient technique for multi-target test generation using concolic testing is proposed. It fully utilizes information from the previous search. Specifically, this approach improves the overall performance by the following optimizations: (i) efficient pruning of targets that can be covered by the tests generated for activating other targets, (ii) clustering of related targets to drastically reduce the test generation time, where targets in the same cluster usually share a common simulated path, and (iii) a novel edge realignment technique to effectively evaluate the distance between a simulated path and a target.

Assertion Coverage by Concolic Testing: While existing test generation using model checking is promising in activating assertions, it cannot generate directed tests for large designs due to the state space explosion problem. I propose an automated and scalable mechanism to generate directed tests using a combination of symbolic execution and concrete simulation of RTL models. The proposed methodology consists of two major steps. The first step converts these assertions to branch statements and embeds them into the design. Then, it utilizes

26

concolic testing to generate a compact test set to efficiently cover (activate) the target branches (assertions). The generated test vectors are guaranteed to activate the corresponding assertions non-vacuously. Compared to the exponentially growing memory requirements in model checking, the memory requirement grows linearly in the proposed approach.

Scalable Cache Coherence Protocol Validation: To address the scalability concerns in validating FSM of cache coherence protocols with many cores, my research combines on-the-fly test generation technique [35] with a quotient space based approach. This approach first analyzes the state space structure of their corresponding global FSMs and decomposes them into several components with simple structures. Then, it utilizes the symmetric structure of protocol state space to efficiently cover all states and transitions. Next, quotient space based scalable test generation algorithms trade-off between functional coverage and verification effort to cover important state transitions within limited verification budget. Quotient space guarantees selection of important transitions by utilizing equivalence classes, and omits only similar transitions to provide scalable test generation framework. The experimental results demonstrated the effectiveness on systems with many cores and complex cache coherence protocols, making it suitable for future multi-core architectures.

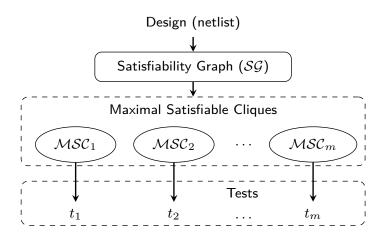

Trigger Coverage using Clique Cover: Trigger activation is a major challenge due to the exponentially large space that an adversary can exploit to construct trigger conditions. Conventional validation approaches using millions of random test vectors or ATPG test vectors are not effective in activating extremely rare and unknown trigger conditions. To address the fundamental challenge of activating rare triggers, I propose a new test generation paradigm for Trigger Activation by Repeated Maximal Clique sampling (TARMAC). The basic idea is to utilize a satisfiability modulo theories (SMT) solver to construct a test corresponding to each maximal clique. It makes three fundamental contributions: (1) it proves that the trigger activation problem can be mapped to clique cover problem, and the test vectors generated by covering maximal cliques are complete and compact, (2) it proposes efficient test generation algorithms to activate trigger conditions by repeated maximal clique sampling, and (3) it

outlines an efficient mechanism to run the clique sampling in parallel to significantly improve the scalability of our test generation framework.

Current-based Side-Channel Analysis: I propose an efficient test generation technique to facilitate side-channel analysis utilizing dynamic current. My proposed approach effectively searches for efficient tests that can drastically improve the side-channel sensitivity - making Trojan detection feasible in practice. To increase the overall sensitivity, my approach exploits the input affinity to identify test patterns that can maximize switching in the suspicious (target) region while minimize switching in the rest of the circuit in order to significantly improve the side-channel sensitivity. This approach shows significant improvement in sensitivity to detect the majority of Trojans, while the state-of-the-art approaches can detect less than 1% Trojans.

Delay-based Side-Channel Analysis: Existing delay-based side-channel analysis techniques have two major bottlenecks: (i) they are not suitable in detecting Trojans since the delay difference between the golden design and a Trojan inserted design is negligible, and (ii) they are not effective in creating robust delay signatures due to reliance on random and ATPG based test patterns. In this dissertation, I propose an efficient test generation technique to detect Trojans using delay-based side channel analysis. First, I design a lightweight and effective logic testing algorithm to generate tests for delay-based side-channel analysis. The generated tests assume no preliminary information about critical paths or trigger conditions. Next, I perform a Hamming-distance based reordering of the generated tests. The reordering is based on a distance evaluation method that can increase the probability of constructing a critical path from the trigger to the payload.

#### 1.4 Dissertation Organization

The rest of this dissertation is organized as follows. Chapter 2 surveys existing security validation approaches. In Chapter 3, a wide variety of common SoC security vulnerabilities are identified and their corresponding classes of assertions are proposed. Chapter 4 describes an automated test generation technique for activating multiple targets in RTL models using

Figure 1-14. Dissertation outline.

concolic testing. Chapter 5 shows how concolic testing can be applied to RTL models to activate assertions. Chapter 6 presents a scalable on-the-fly test generation technique to validate the FSM of cache coherence protocols. Chapter 7 demonstrates an effective test generation approach to activate trigger conditions by mapping it to the problem of clique covering. Chapter 8 and Chapter 9 describe an efficient test generation technique for detecting hardware Trojans using dynamic current and path delay, respectively. Finally, Chapter 10 concludes this dissertation.

# CHAPTER 2 BACKGROUND AND RELATED WORK

There are extensive research efforts for hardware security validation. These approaches can be broadly classified into three categories: formal methods, simulation-base validation, and side-channel analysis. This chapter reviews these existing approaches that are related to this dissertation.

# 2.1 SoC Security Validation using Formal Methods

Instead of relying on the quality of generated tests to reveal the vulnerabilities in a design, formal methods utilizes mathematical models to verify that the design (implementation) satisfies its specification. There are four widely used forms of formal verification methods.

- Satisfiability solving determines if a given Boolean formula can be true. There are many validation problems that can be converted into satisfiability problem. For example, to validate if an implementation is equivalent to its specification, a Boolean formula can be constructed by computing (XOR) of the functional outputs of these two designs. If the SAT solver returns assignments to the variables that make the formula to be true, the implementation and the specification are different.

- Equivalence checking [9, 36, 37] verifies if two designs are equivalent or not. There are two common types of techniques for equivalence checking. The first type utilizes model checking to verify the equivalence using Binary Decision Diagrams (BDDs). The other type utilizes SAT solvers to return a counter-example if the two designs are different by converting the designs to Conjunctive Normal Form (CNF).

- Property checking [38] verifies if a design satisfies a set of properties. The design and properties are first converted to formal languages. Both the design and the properties are fed into a model checker. The model checker either finds a counter-example or proves that the property holds in the design. Property checking can be implemented using BDDs as well as SAT-based bounded model checking.

- Theorem proving [39] builds mathematical formulas to represent the behavior of a design (implementation) and evaluate these formulas against a specific requirement (security specification). It needs to formulate a theorem to describe the requirement. Next, it needs to prove the theorem using a set of axioms and facts that can be derived from the specification.

#### 2.2 SoC Security Validation using Simulation-based Validation

Simulation-based validation aims at developing tests to simulate the design and achieve high coverage goals. There are different methods to generate tests, including

random/constrained-random approaches, directed testing generation using formal methods, statistical methods, and concolic testing which interleaves simulation and formal methods.

# 2.2.1 Random/Constrained-Random Simulation

Simulation using random and constrained-random tests is widely used in both industry and academia due to its good scalability. For example, random/constrained-random approaches are widely used to validate the states and transitions in FSM. Wood et al. [40] used random tests to verify the memory subsystem of SPUR machine. Genesys Pro test generator [41] from IBM extended this direction with complex and sophisticated test templates. To reduce the search space, Abts et al. [42] introduced space pruning technique during their verification of the Cray processor. Wagner et al. [11] designed the MCjammer tool which can get higher state coverage than normal constrained random tests. Since an uncovered transition can only be visited by taking a unique action at a particular state, it may not be feasible for a random test generator to eventually cover all possible states and transitions. To address this problem, some random testers are equipped with a small amount of memory, so that the future search can be guided to the uncovered regions. Unfortunately, unless the memory is large enough to hold the entire state space, it is hard to achieve full coverage by such guided random testing.

## 2.2.2 Directed Test Generation using Formal Methods

In spite of the fast test generation time in random and constrained-random approaches, their coverage/performance is poor. Validation using billions or trillions of random tests cannot provide 100% coverage. The uncovered scenarios will likely be hard-to-detect (rare) branches and corner-case scenarios in today's industrial designs. Verification engineers usually write specific (directed) test cases manually to cover the remaining hard-to-activate scenarios such as corner cases and rare events. While manual test development is possible for small designs, it would be infeasible to develop directed tests manually for complex SoC designs. Moreover, manual development of test cases can be both error-prone and time-consuming due to many trial-and-error iterations in complex designs. Automated test generation is necessary to overcome these issues.

Formal methods, such as model checking [4, 35, 43–45], is effective in automated generation of directed tests for property checking. To activate a specific target (functional behavior), the negated version of a property (functional behavior) is fed into a model checker, which will return a counterexample as the test that can activate the target. Binary Decision Diagrams (BDD) based BMC [46] and SAT-based BMC [38] are two widely used model checking methods [47]. From non-deterministic finite automata (NFA), Tong et al. [44] utilized model checking to generate test for assertions with the assumption that the signals in assertions refer to the primary inputs. This type of approaches have a few bottlenecks. In order to enable test generation, they restrict the assertions to have variables of only specific types (e.g., primary inputs). Model checking is also used to validate the correctness of a cache coherence protocol. It can prove mathematically whether the description of certain protocol violates a required property [48].

There are two major problems in applying formal methods directly to the design. First, formal methods expect formal specification and require translation from specifications or Hardware Description Language (HDL) models to their supported formats. The extra procedure of conversion to formal specification may introduce errors. Second, the complexity of real world designs usually exceeds the capacity of the model checking tools, leading to state space explosion. Extensive research has been devoted to reduce the model checking complexity during test generation using various design/property decomposition as well as learning techniques [35, 49, 50]. In spite of these extensive efforts, it is infeasible to generate directed tests using model checking based approaches due to inherent state explosion problem while dealing with complex properties as well as large designs.

#### 2.2.3 Statistical Methods

Logic testing [12, 51–54] is the main approach to detect hardware Trojans by comparing the outputs of an implementation to a golden specification. ATPG based logic testing is an effective method to find tests of a design using fault simulation. With the help of Design-for-Testability (DfT) structures, such as scan chain, ATPG treats all sequential logic