#### FORMAL VERIFICATION OF HARDWARE SECURITY AND TRUST

# By FARIMAH FARAHMANDI

A DISSERTATION PRESENTED TO THE GRADUATE SCHOOL OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

UNIVERSITY OF FLORIDA

2018

$\odot$  2018 Farimah Farahmandi

#### ACKNOWLEDGMENTS

First of all, I really appreciate my adviser Prof. Prabhat Mishra for what he has done for me. It was him who led me to open the door of computer science. I will never forget all his kind instructions and enduring support. He not only guided me to overcome challenging problems, but also taught me how to explore new directions. More importantly, he is always considerate to me and has helped me building my own career. He is the person who made this dissertation come true.

I would also like to thank my other Ph.D. committee members: Prof. Sartaj Sahni, Prof. Sanjay Ranka, Prof. Nima Maghari for their precious advises and criticisms. I appreciate Prof. Sandip Ray with whom I collaborated for one year. His profound knowledge in post-silicon validation and debug helped me a lot in my research. I am also thankful for the collaboration with Prof. Domenic Forte and Prof. Mark Tehranipoor.

I also thank my lab-mates, Yuanwen Huang, Alif Ahmed, , Yangdi Lyu, Subodha Charles, and Jonathan Cruz. It was my great pleasure to work with them. I really enjoyed our friendship and I hope it will last forever.

Last but not least, I sincerely thank my mother, father, and my lovely sisters (Farzaneh and Fargol) for their love, encouragement and support. I wouldn't be able to achieve anything without my parents' raising since my childhood. Their all-embracing love and care – guiding me patiently, supporting my decisions, forgiving my faults – makes me grow up freely. I want to thank my beautiful friend, Roshanak, who has been always by my side and help me a lot. My most special appreciation is dedicated to my Husband, Matin, his love and devotion paved the road to my doctoral degree. He always holds my hands and gives me courage whenever I need. I have realized how lucky I am to have him.

### TABLE OF CONTENTS

|      |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | page                                                           |

|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| ACK  | NOV               | VLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                              |

| LIST | OF                | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                              |

| LIST | OF                | FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9                                                              |

| ABS' | TRA               | CT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11                                                             |

| СНА  | PTE               | m R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |

| 1    | INT               | RODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12                                                             |

|      | 1.1<br>1.2<br>1.3 | Security Validation: Opportunities and Challenges  1.1.1 Pre-Silicon Trust Validation  1.1.2 Post-synthesized Non-functional Changes versus Security  1.1.3 Control Flow Integrity Measurement  1.1.4 Test Generation to Activate Trojans  1.1.5 Functional Coverage Analysis of Security Properties  Research Contributions  Dissertation Organization                                                                                                                                                 | 15<br>16<br>18<br>19<br>20<br>22<br>23<br>28                   |

| 2    | REL               | ATED WORK ON SECURITY VALIDATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                             |

|      | 2.2               | Simulation-based Trust Validation Approaches  2.1.1 Functional Test Generation  2.1.2 Statistical Methods  2.1.3 Side-Channel Analysis  Security validation using Formal methods  2.2.1 Trust Validation using SAT Solvers  2.2.2 Security Validation using Property Checking  2.2.3 Theorem Provers for Trojan Detection  2.2.3.1 Secret Data Protection using Proof-Carrying Codes  2.2.3.2 Integration of Theorem Provers and Model Checkers  2.2.4 Trojan Detection using Symbolic Algebra  Summary | 29<br>30<br>31<br>32<br>33<br>36<br>42<br>42<br>45<br>46<br>47 |

| 3    | BAC               | CKGROUND: VERIFICATION USING SYMBOLIC ALGEBRA                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48                                                             |

|      | 3.1<br>3.2<br>3.3 | Gröbner Basis Theory Verification of Arithmetic Circuits Summary                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48<br>53<br>55                                                 |

| 4    | ANC               | DMALY DETECTION AND CORRECTION IN ARITHMETIC CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56                                                             |

|      | 4.1               | Automated Debugging using Remainders                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58<br>60                                                       |

|   |     | 4.1.2 Bug Localization                                      | $6^{2}$ |

|---|-----|-------------------------------------------------------------|---------|

|   |     | 4.1.3 Error Detection and Correction                        | 64      |

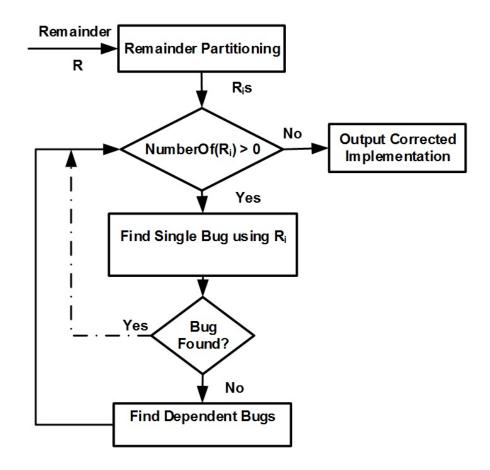

|   | 4.2 | Debugging Multiple Bugs                                     | 68      |

|   |     | 4.2.1 Error Correction for Multiple Independent Bugs        | 71      |

|   |     | 4.2.2 Error Correction for Two Bugs with Common Input Cones | 73      |

|   | 4.3 | Experiments                                                 | 78      |

|   |     | 4.3.1 Experimental Setup                                    | 78      |

|   |     | 4.3.2 Debugging a Single Error                              | 79      |

|   |     | 4.3.3 Debugging Multiple Errors                             | 81      |

|   | 4.4 | Summary                                                     | 83      |

| 5 | INC | REMENTAL ANOMALY DETECTION                                  | 85      |

|   | 5.1 | Efficient Debugging of Arithmetic Circuits                  | 86      |

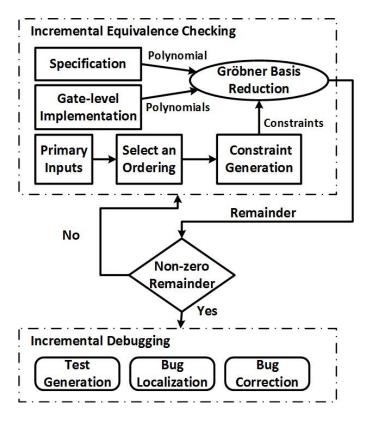

|   | 0.1 | 5.1.1 Incremental Equivalence Checking                      | 87      |

|   |     | 5.1.2 Ordering of Primary Inputs                            | 93      |

|   |     | 5.1.3 Incremental Debugging                                 | 94      |

|   | 5.2 | Experiments                                                 | 96      |

|   |     | 5.2.1 Experimental Setup                                    | 96      |

|   |     | 5.2.2 Results                                               | 97      |

|   | 5.3 |                                                             | 100     |

| 6 | TRO | DJAN LOCALIZATION USING SYMBOLIC ALGEBRA                    | 101     |

|   | 6.1 | Traign Detection and Localization                           | 102     |

|   | 0.1 | ů                                                           | 102     |

|   |     |                                                             | 100     |

|   |     |                                                             | 100     |

|   | 6.2 |                                                             | 111     |

|   | 0.2 |                                                             | 111     |

|   |     | 1                                                           | 112     |

|   |     |                                                             | 114     |

|   | 6.3 |                                                             | 115     |

|   |     |                                                             |         |

| 7 | FSN | I INTEGRITY ANALYSIS IN CONTROLLER DESIGNS                  | 117     |

|   | 7.1 |                                                             | 120     |

|   | 7.2 | · · · · · · · · · · · · · · · · · · ·                       | 122     |

|   |     | 7.2.1 Deriving Specification Polynomials                    | 123     |

|   |     | 7.2.2 Generation of Implementation Polynomials              | 127     |

|   |     | 1                                                           | 129     |

|   | 7.3 | •                                                           | 132     |

|   |     | · · · · · · · · · · · · · · · · · · ·                       | 132     |

|   |     |                                                             | 132     |

|   | 7.4 | Summary                                                     | 134     |

| 8  | TROJAN ACTIVATION BY INTERLEAVING CONCRETE SIMULATION AND SYMBOLIC EXECUTION                                                                                                                                                                                                                                  | 136                                                                |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|    | Threat Model                                                                                                                                                                                                                                                                                                  | 138<br>138<br>140<br>141<br>142<br>144                             |

|    | 8.4.1 Experimental Setup                                                                                                                                                                                                                                                                                      | 146<br>146<br>147<br>148<br>148                                    |

|    | 8.5 Summary                                                                                                                                                                                                                                                                                                   | 151                                                                |

| 9  | OBSERVABILITY-AWARE POST-SILICON TEST GENERATION                                                                                                                                                                                                                                                              | 152                                                                |

|    | 9.1.1 Mapping Observability Constraints                                                                                                                                                                                                                                                                       | 152<br>153<br>156<br>157<br>158                                    |

|    | 9.2 Case Studies                                                                                                                                                                                                                                                                                              | 158<br>158<br>159<br>160                                           |

| 10 | COVERAGE OF SECURITY PROPERTIES IN RUN-TIME                                                                                                                                                                                                                                                                   | 161                                                                |

|    | 10.2 Post-Silicon Functional Coverage Analysis  10.2.1 Decomposition of Coverage Scenarios  10.2.2 Restoration of Signal States  10.2.3 Coverage Analysis  10.2.4 Coverage-aware Signal Selection  10.3 Experiments  10.3.1 Experimental Setup  10.3.2 Results  10.3.3 Observability versus Hardware Overhead | 163<br>165<br>165<br>169<br>170<br>173<br>174<br>174<br>175<br>176 |

| 11 | CONCLUSIONS AND FUTURE RESEARCH DIRECTIONS                                                                                                                                                                                                                                                                    | 180                                                                |

|    | 11.1 Future Research Directions                                                                                                                                                                                                                                                                               | 184                                                                |

| Δ  | LIST OF PURLICATIONS                                                                                                                                                                                                                                                                                          | 187                                                                |

| REFERENCES          | 190 |

|---------------------|-----|

| BIOGRAPHICAL SKETCH | 202 |

## LIST OF TABLES

| Table | $\frac{\mathrm{e}}{\mathrm{e}}$                                                   | page |

|-------|-----------------------------------------------------------------------------------|------|

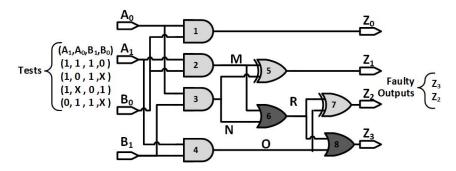

| 4-1   | Directed tests to activate fault shown in Fig. 4-4                                | 62   |

| 4-2   | Remainder patterns caused by gate misplacement error                              | 65   |

| 4-3   | Patterns for potential faulty gates Example 11                                    | 77   |

| 4-4   | Results for Debugging One Error in Arithmetic Circuits                            | 79   |

| 4-5   | Test Generation for 4-bit multiplier with 8-bit outputs                           | 80   |

| 4-6   | Debugging time of multipliers for multiple independent bugs                       | 82   |

| 4-7   | Debugging time of multipliers for two dependent bugs                              | 83   |

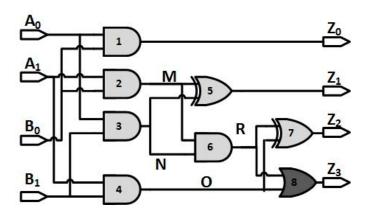

| 5-1   | Different constraints on primary inputs of a 2-bit multiplier                     | 90   |

| 5-2   | Input constraints to debug faulty circuit                                         | 93   |

| 5-3   | Templates can be caused by gate misplacement error                                | 95   |

| 5-4   | Results of the incremental equivalence and debugging approaches                   | 98   |

| 5-5   | The equivalence checking time for correct designs                                 | 100  |

| 6-1   | Trojan Localization using Trust-HUB benchmarks                                    | 112  |

| 6-2   | The required tests to activate the Trojan                                         | 114  |

| 7-1   | Malicious access paths to the protected state $O$ shown in Figure 7-2             | 131  |

| 7-2   | Result for FSM Anomaly detection technique                                        | 133  |

| 8-1   | EBMC results to generate directed tests that activate Trojans                     | 148  |

| 8-2   | Time and memory results to activate Trojans using Concolic testing                | 149  |

| 9-1   | Test generation's time for safety properties in network with four switches        | 159  |

| 9-2   | Test Generation's Time for safety properties in a pipelined processor             | 160  |

| 10-1  | Restored signals for circuit shown in Figure 10-1 when A and B are trace signals. | 172  |

| 10-2  | Result for assertion coverage                                                     | 177  |

| 10-3  | Assertion coverage using trace buffer information                                 | 177  |

# LIST OF FIGURES

| Figu | <u>pa</u>                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>ige</u> |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1-1  | An SoC design integrates a wide variety of IPs in a chip. It can include one or more processor cores, on-chip memory, digital signal processor (DSP), analog-to-dig (ADC), and digital-to-analog converters (DAC), controllers, input/output periphera and communication fabric. Huge complexity, many custom designs, distributed supply chain and integration of untrusted third-party IPs make post-silicon validational challenging. | ıls,       |

| 1-2  | Hardware trust verification can be categorized in three major directions: i) high-lever modeling using polynomials, ii) generation of tests, assertions and properties for post-silicon security validation, and iii) effective utilization of pre-silicon efforts for post-silicon debug                                                                                                                                                | el<br>15   |

| 1-3  | Potential threats during SoC design flow                                                                                                                                                                                                                                                                                                                                                                                                 | 17         |

| 1-4  | Comprehensive nature of my research                                                                                                                                                                                                                                                                                                                                                                                                      | 23         |

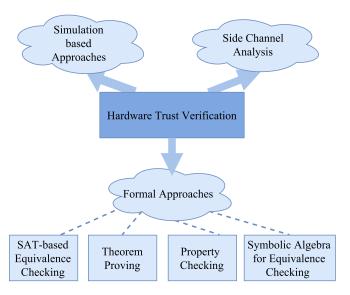

| 2-1  | Hardware trust verification can be categorized in three major directions: (1) simulation based approaches, (2) side-channel analysis, and (3) formal approaches.                                                                                                                                                                                                                                                                         | 29         |

| 2-2  | Equivalence checking using SAT solvers                                                                                                                                                                                                                                                                                                                                                                                                   | 34         |

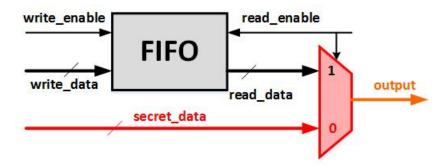

| 2-3  | Trojan in unspecified functionality of a FIFO [56]                                                                                                                                                                                                                                                                                                                                                                                       | 35         |

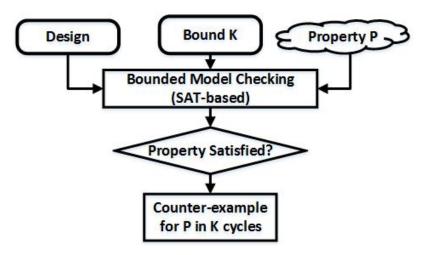

| 2-4  | Verification using model checking                                                                                                                                                                                                                                                                                                                                                                                                        | 37         |

| 2-5  | Verification using bounded model checking                                                                                                                                                                                                                                                                                                                                                                                                | 38         |

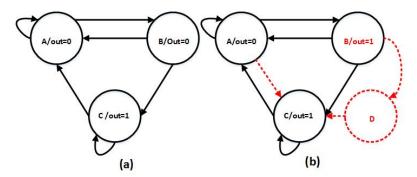

| 2-6  | Trojans in a FSM: (a) A Trojan-free FSM, (b) Trojan can be inserted to a FSM using different ways: (i) changing the state output (e.g. state $B$ ), (ii) modification to state transitions (e.g. extra transition from state $A$ to $C$ ), and (iii) adding extra states (e.g. state $D$ ) and transitions (such as state transitions $B \to D$ and $D \to C$ ) to FSM                                                                   | 41         |

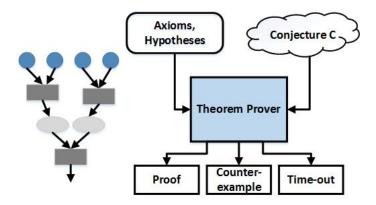

| 2-7  | Validation using theorem Prover                                                                                                                                                                                                                                                                                                                                                                                                          | 43         |

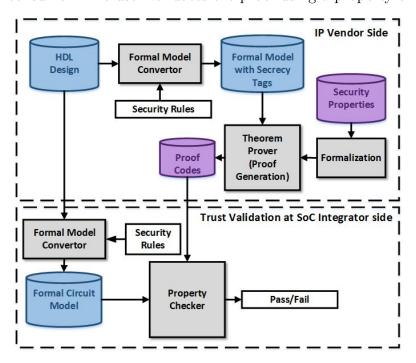

| 2-8  | Information flow tracking based on proof-carrying codes                                                                                                                                                                                                                                                                                                                                                                                  | 44         |

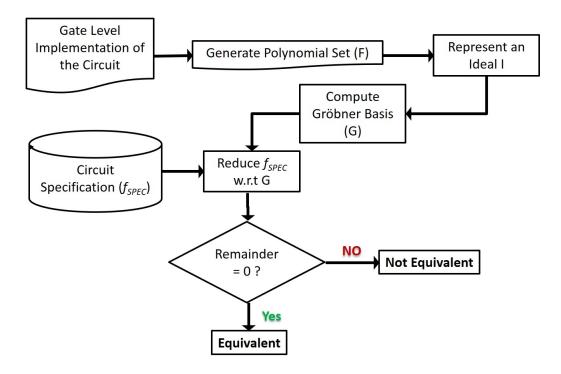

| 3-1  | Equivalence checking flow                                                                                                                                                                                                                                                                                                                                                                                                                | 51         |

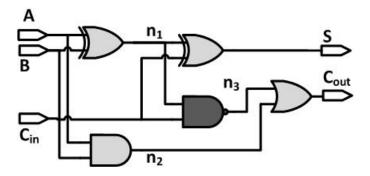

| 3-2  | Faulty gate-level netlist of a full-adder. The NAND gate should be replaced by an AND gate to correct the bug.                                                                                                                                                                                                                                                                                                                           | 55         |

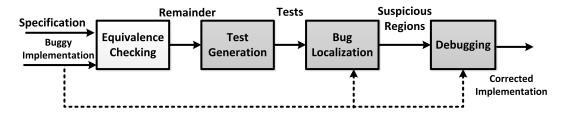

| 4-1  | Overview of our automated debugging framework                                                                                                                                                                                                                                                                                                                                                                                            | 57         |

| 4-2  | Relative bugs' locations and their corresponding input cones of influence                                                                                                                                                                                                                                                                                                                                                                | 58         |

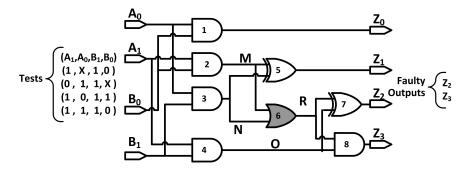

| 4-3  | Overview of different steps to debug multiple bugs                                                                                                                                                                                                                                                                                                                                                                                       | 59         |

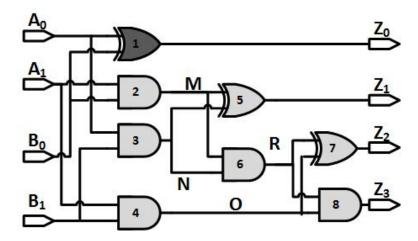

| 4-4  | Faulty gate-level netlist of a 2-bit multiplier                                | 60  |

|------|--------------------------------------------------------------------------------|-----|

| 4-5  | Faulty gate-level netlist of a 2-bit multiplier with associated tests          | 64  |

| 4-6  | Overview of different steps of our proposed debugging framework                | 69  |

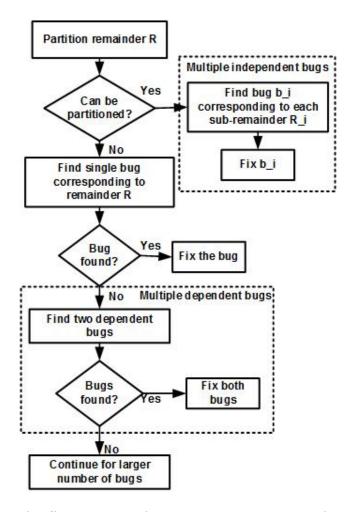

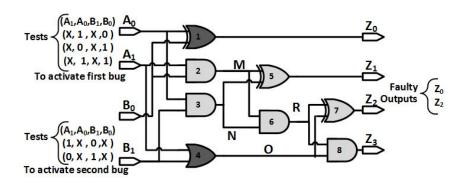

| 4-7  | Gate-level netlist of a 2-bit faulty multiplier                                | 70  |

| 4-8  | Gate-level netlist of a 2-bit multiplier with two bugs                         | 75  |

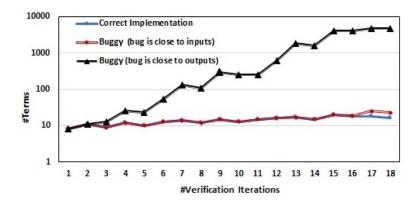

| 5-1  | Comparison of the number of terms in different iterations of verification      | 86  |

| 5-2  | Overview of our proposed approach.                                             | 87  |

| 5-3  | Faulty netlist with one bug (gate 8 should have been an AND)                   | 89  |

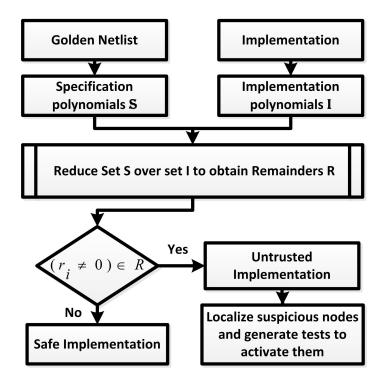

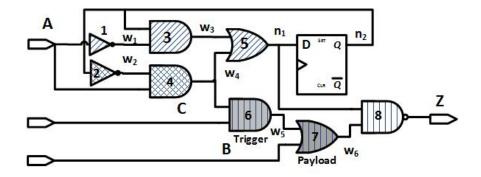

| 6-1  | The proposed hardware Trojan localization flow                                 | 102 |

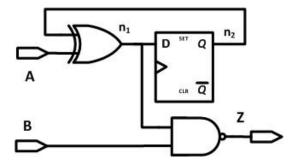

| 6-2  | A part of a sequential circuit                                                 | 10  |

| 6-3  | A Trojan-inserted implementation of circuit in Figure 6-2                      | 106 |

| 6-4  | (a) Number of suspicious nodes, (b) Number of tests needed to activate Trojans | 111 |

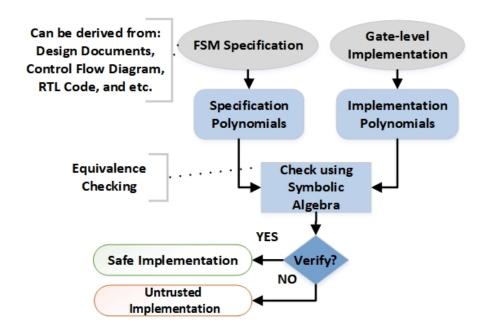

| 7-1  | Overview of FSM anomaly detection approach                                     | 119 |

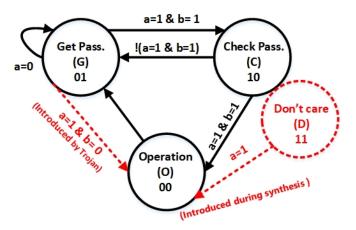

| 7-2  | State diagram for checking a password to perform a specific operation          | 122 |

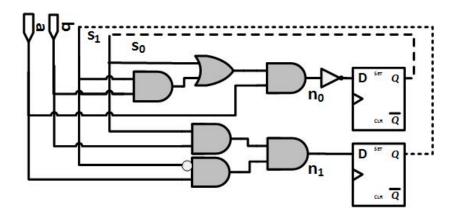

| 7-3  | Implementation of FSM in Figure 7-2 using binary encoding                      | 128 |

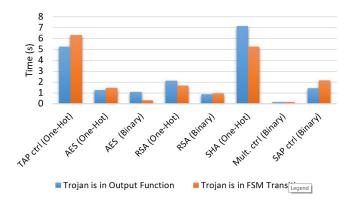

| 7-4  | Time required to detect hardware Trojans in FSMs' outputs                      | 134 |

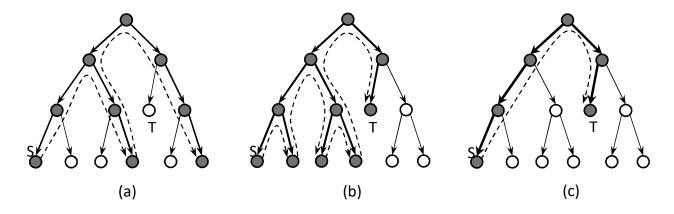

| 8-1  | CFG traversal of different test generation methods                             | 139 |

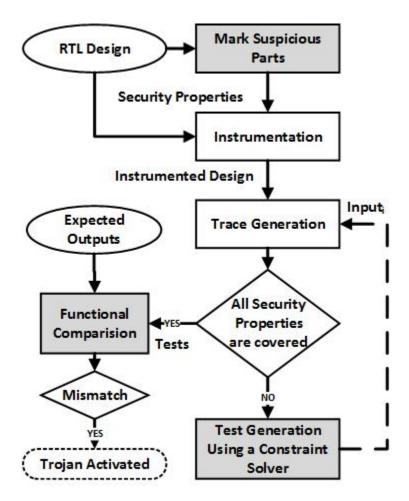

| 8-2  | Proposed hardware Trojan activation framework                                  | 141 |

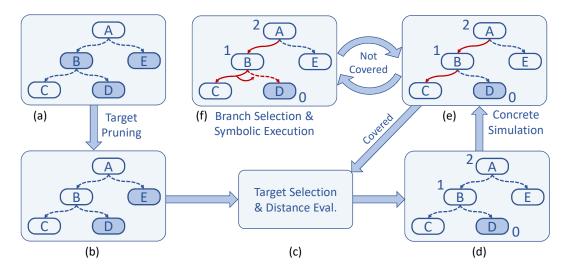

| 8-3  | Overview of test generation procedure                                          | 146 |

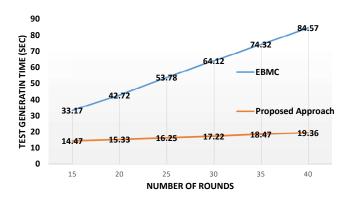

| 8-4  | Test generation time to activate the Trojan in $cb\_aes\_xx$ benchmarks        | 150 |

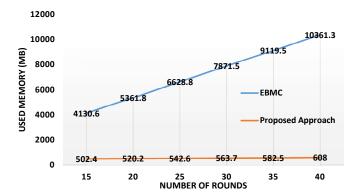

| 8-5  | Memory requirement to activate the Trojan in $cb\_aes\_xx$ benchmarks          | 150 |

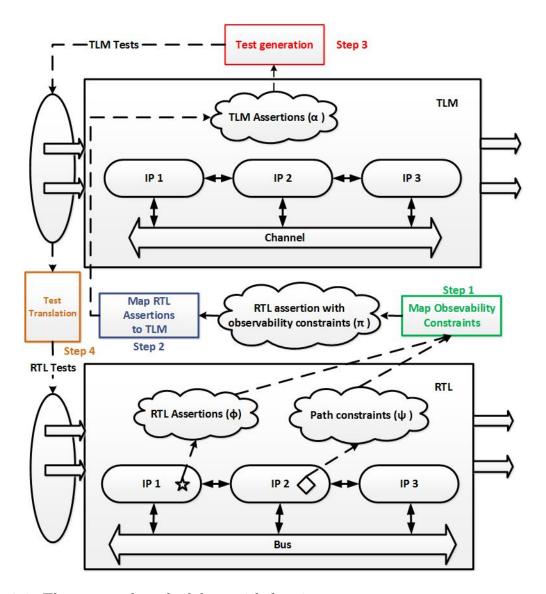

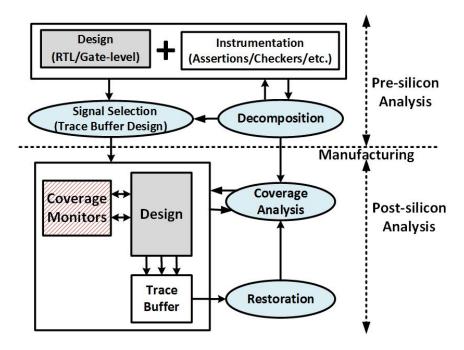

| 9-1  | The proposed methodology with four important steps                             | 154 |

| 9-2  | Router design, RTL and TLM implementations                                     | 155 |

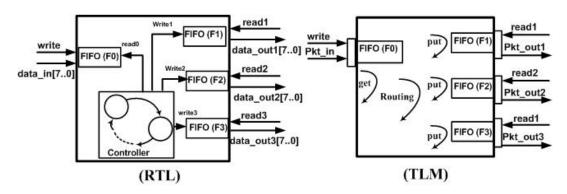

| 10-1 | A simple circuit to illustrate design properties                               | 16  |

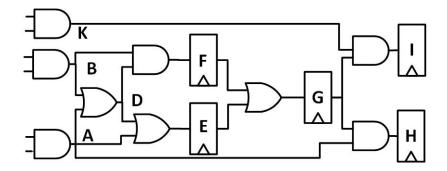

| 10-2 | Overview of our proposed approach                                              | 166 |

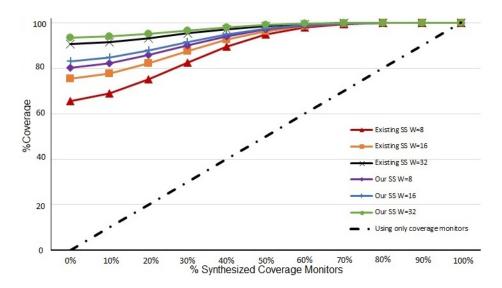

| 10-3 | Coverage analysis for s9234: coverage monitors are selected randomly           | 178 |

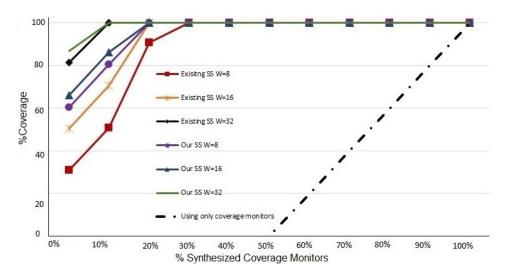

| 10-4 | Coverage analysis for s9234: coverage monitors are from hard-to-detect events  | 179 |

Abstract of Dissertation Presented to the Graduate School of the University of Florida in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

#### FORMAL VERIFICATION OF HARDWARE SECURITY AND TRUST

By

#### Farimah Farahmandi

April 2018

Chair: Prabhat Mishra

Major: Computer Engineering

Trust establishment in semiconductor designs has become a major challenge for design houses and government since several countries and companies are involved during different stages of a design life cycle. Hardware Trojans are malfunctions which can be inserted during any design stage such as defining specification, implementing designs at different abstraction levels, layout extraction and manufacturing. A triggered hardware Trojan can severely affect the integrity and security of the circuit by causing system failures such as granting an unauthorized access to secret information. Hardware Trojans are designed in a way that they are inactive most of the time and can be triggered with a very rare input sequence. Therefore, conventional validation techniques are not effective to detect them because of the Trojan's stealthy nature. Formal methods are promising to prove the security properties; however, the conventional formal methods suffer from scalability concerns. In this dissertation, I propose scalable hardware trust validation techniques using formal methods. I have developed an automated test generation and debugging framework using Gröbner basis reduction for arithmetic circuits. For pre-silicon designs, I have shown that symbolic algebra can be effectively used for localizing hardware Trojans. I have also developed efficient post-silicon trust validation techniques by leveraging pre-silicon verification effort. The experimental results demonstrate that the proposed approaches are scalable in establishing that the implementation has "nothing more, nothing less" compared to the golden specification.

11

#### CHAPTER 1 INTRODUCTION

People have embraced a wide variety of mobile devices in their daily lives in addition to their traditional desktop computers and laptops. Considering the fabric of Internet of Things (IoT) [115], where the number of connected devices exceeds the human population, we should all agree to the fact that computing devices pervade every aspect of our lives. In IoT devices, integrated electronics, sensors, sophisticated software and firmware, and learning algorithms are employed to make physical objects smart and adjustable to their environment. These highly complex and smart IoT devices are embedded everywhere - starting from household items (e.g., refrigerators, slow cookers, ceiling fans), wearable devices (e.g., fitness trackers, smart glasses, air bugs), medical devices (e.g., insulin pump, asthma monitoring, ventilator) to cars. These IoT devices are connected to each other as well as cloud in order to provide a real-time aid on a daily basis. Given the diverse and critical applications of these computing devices, it is crucial to verify the correctness, security and reliability of these devices.

Modern computing devices are designed using System-on-Chip (SoC) technology. In other words, SoC is the backbone for most of the IoT devices. Sheer complexity of the System-on-Chip (SoC) designs used in these systems combined with diverse and evolving use cases make product security assurance a major challenge. Effective and well-developed security validation is an important and integral part of the security assurance process today. However, existing security verification approaches both pre- and post-silicon are often ad-hoc and manual (i.e. rely on human ingenuity and experience). There is a critical need to identify all possible security vulnerabilities and fix them using an automatic and reliable mechanism during security validation. Attacks on hardware can be more effective and efficient than traditional software attacks since patching is extremely difficult (almost impossible) on hardware designs. Therefore, a security attack can be successfully repeated on every instance of a vulnerable IoT device. In other words, hardware level

vulnerabilities are extremely important to be fixed before deployment since it affects the overall system security. Based on Common Vulnerability Exposure (CVE-MITRE) estimates, if hardware-level vulnerabilities are removed, the overall system vulnerability will reduce by 43% [67, 68].

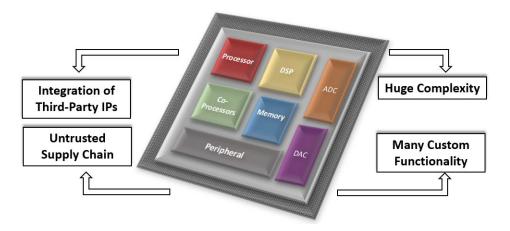

Figure 1-1. An SoC design integrates a wide variety of IPs in a chip. It can include one or more processor cores, on-chip memory, digital signal processor (DSP), analog-to-digital (ADC), and digital-to-analog converters (DAC), controllers, input/output peripherals, and communication fabric. Huge complexity, many custom designs, distributed supply chain and integration of untrusted third-party IPs make post-silicon validation challenging.

An SoC architecture typically consists of several pre-designed Intellectual Property (IP) blocks, where each IP implements a specific functionality of the overall design. Figure 1-1 shows a typical SoC with its associated IPs. These IPs communicate with each other through Network-on-Chip (NoC) or standard communication fabrics. The IP-based design approach is popular today since it enable a low-cost design while meeting stringent time-to-market requirements. With the globalization of the IC industry, the outsourcing and integration of third-party hardware IPs (Intellectual Property) has become a common practice for System-on-Chip (SoC) design [17, 51]. However, it raises major security concerns as the attacker can insert malicious modifications in third-party IPs and tamper the system. Security vulnerabilities can be inserted in high-level specification (e.g., TLM and RTL models) in synthesized gate-level netlist, layouts as well as in the fabricated

chip by an attacker. It is extremely important to differentiate trustworthy designs from untrustworthy ones by detecting any potential malicious functionality (widely known as hardware Trojans), which is not in the design specification. Hardware Trojans consist of two main parts: trigger and payload. The trigger is a condition which activates the Trojan circuit and the payload is the part of the circuit (functionality) which can be affected by an activated Trojan. A triggered Trojan may endanger the integrity of the design by leaking critical information such as secret keys or causing denial of service.

A major challenge for Trojan identification is that Trojans are usually stealthy [17]. It is difficult to construct a fault model to characterize Trojan's behavior. Moreover, Trojans are designed in a way that they can be activated under very rare conditions and they are hard-to-detect. Therefore, it is difficult to activate a Trojan and even more difficult to detect or locate it. As a result, conventional validation methods are impractical to detect hardware Trojans. Conventional structural and functional testing methods are not effective to activate trigger conditions since there are many possible Trojans and it is not feasible to construct a fault model for each of them. As a result, existing EDA tools are incapable of detecting hardware Trojans to differentiate between trustworthy third-party IPs and untrusted ones.

There has been a lot of research on hardware Trojan detection using logic testing and side channel analysis [2, 30, 76]. Logic testing focuses on generating efficient tests to activate a Trojan and check the primary output values of specification and circuit-under-test to detect Trojan. On the other hand, side channel analysis compares signatures of specific physical characteristics (e.g., dynamic current) between the design and the golden specification. However, none of these methods can effectively establish the trust for a given design. Therefore, it is crucial to have methods that can detect, localize and eliminate the Trojan, and produce Trojan-free circuits. Formal methods are suitable for detecting and localizing Trojans during the design phase. In this dissertation, I focus on different formal methods to verify the design and detect undesired functions (possibly

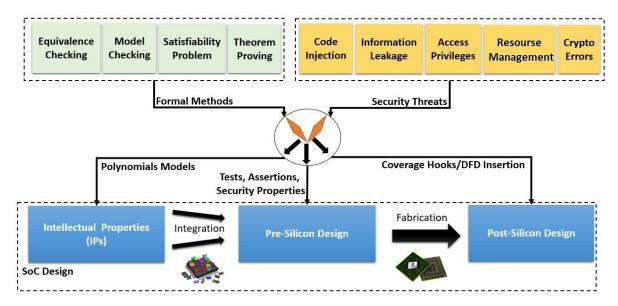

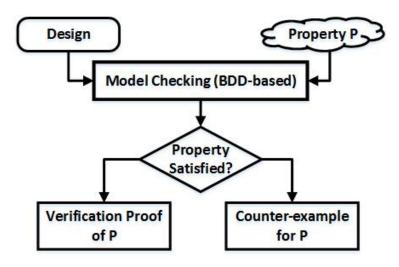

Trojans). As shown in Figure 2-1, I proposed trust validation based on Formal methods that includes efficient test generation using property (model) checking, satisfiability problem, equivalence checking and reaching effective coverage closures in post-silicon.

Figure 1-2. Hardware trust verification can be categorized in three major directions: i) high-level modeling using polynomials, ii) generation of tests, assertions and properties for post-silicon security validation, and iii) effective utilization of pre-silicon efforts for post-silicon debug.

The rest of this chapter is organized as follows. Section 1.1 describes the security vulnerabilities in current hardware design flow as well as associated challenges to validate them. Section 1.2 summarizes the contributions of this dissertation. Finally, Section 1.3 describes the organization of this dissertation.

#### 1.1 Security Validation: Opportunities and Challenges

From specification to silicon, the design will go through different transformations. System on chip design procedure starts with defining the specification. The specification contains all information about the expected behavior of the chip. In the second step, the specification is implemented using programming languages such as Verilog and VHDL. Then, the modules should be synthesized to a gate-level netlist. The gate-level netlist will go through several non-functional changes for different purposes such as clock-tree insertion, power optimization. The layout of the gate-level netlist is extracted, and the

chip will be fabricated in the final design step. During each of these steps, there may be several security concerns that threaten the integrity of the whole chip. In other words, it is extremely important to make sure that the design is behaving like the specification in each of the steps and each intermediate design forms should be exactly equal to the specification, nothing more, nothing less.

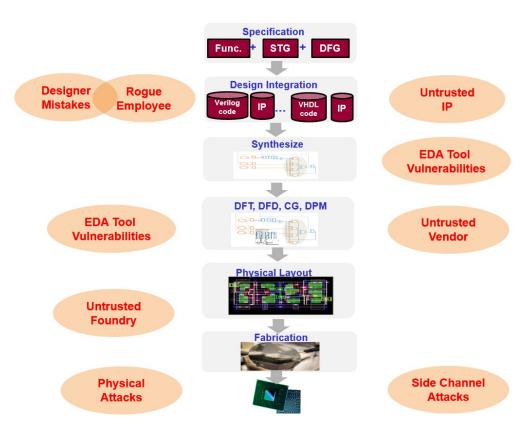

A design can encounter security threats during different stages of its life cycle as shown in Figure 1-3. Security threats can be inserted throughout the IC design as well as manufacturing process. In the pre-silicon stage, vulnerability can be introduced due to (1) designer mistakes, rogue employees, and untrusted third-party IPs during the design integration phase; (2) untrusted EDA tools in the synthesize phase; (3) untrusted EDA tools and untrusted vendors when design for test (DFT), design for debug (DFD), and dynamic power management (DPM) functions are added. In the post-silicon stage, vulnerabilities can come from (1) untrusted foundry during manufacturing and (2) physical attacks or side channel attacks after the chip is shipped. It is of paramount importance to verify the trustworthiness of hardware IPs. Therefore, security validation is the critical part of the design process of digital circuits. In order to trust a design, verification and debugging should be done at each of the stages. In this section, we introduce some of the security validation challenges in both pre- and post-silicon phases.

#### 1.1.1 Pre-Silicon Trust Validation

Any intentional or unintentional design mistakes (bugs or hardware Trojans) may cause security vulnerability in the design. Therefore, a design should be validated thoroughly. However, increasing complexity of integrated circuits increases the probability of Trojans in designs. To make it worse, the reduction in time-to-market puts a lot of pressure on verification and debug engineers to potentially faulty sign-off. The situation gets further exacerbated for arithmetic circuits as the bit blasting is a serious limitation for most of the existing validation approaches. Faster bug localization is one of the most important steps in design validation.

Figure 1-3. Potential threats during SoC design flow.

The urge of high speed and high precision computations increases use of arithmetic circuits in real-time applications such as cryptography operations (to ensure secure computation). Optimized and custom arithmetic architectures are required to meet the high speed and precision constraints. There is a critical need for efficient arithmetic circuit verification and debugging techniques due to error proneness of non-standard arithmetic circuit implementations. Hence, the automated debugging of arithmetic circuits is absolutely necessary for efficient security validation.

A major problem with design validation is that we do not know whether a Trojan exists, and how to quickly detect and fix it. We can always keep on generating random tests, in the hope of activating the bug; however, random test generation is neither scalable nor efficient when designs are large and complex. Existing directed test generation techniques [32, 33] are promising only when the list of faults (bugs) is available. However, they are not applicable when bugs are not known a prior.

Test generation is extremely important for functional validation of integrated circuits. A good set of tests can facilitate the debugging and help the verification engineer to find the source of problems. Test generation techniques can be classified into three different categories: random, constrained-random [3] and directed [32]. Random test generators are used to activate unknown errors; however, random test generation is inefficient when designs are large and complex. Constrained-random test generation tries to guide random test generator towards finding test vectors that may activate a set of important functional scenarios. The probabilistic nature of these constraints may lead to situations which can result in generating inefficient tests. Moreover, constraint generation is not possible when we do not have knowledge about the potential bug. A directed test generator, on the other hand, generates one test to target a specific functional scenario [32, 89]. Clearly, less effort is needed to reach the same coverage goal using directed tests compared to random or constrained-random tests. However, existing directed test generation methods require a fault list or desired functional behaviors that need to be activated [89]. These approaches cannot generate directed tests when the Trojan (faulty scenario) is unknown.

When effective tests are available, the source of Trojan has to be localized. Most of the traditional debugging tools are based on techniques such as simulation, binary decision diagrams (like BDDs,\*BMD [25]) and SAT solvers [7, 97]. However, all of these approaches suffer from state space explosion while dealing with large and complex circuits especially arithmetic circuits. Furthermore, most of these approaches cannot provide concrete suggestions to remove Trojans. It is important to introduce efficient, scalable and fully automated test generation, Trojan localization and debugging framework.

#### 1.1.2 Post-synthesized Non-functional Changes versus Security

After a design is implemented and validated in pre-silicon, the synthesized gate-level netlist will go through several non-functional changes for different purposes such as insertion of post-silicon design-for-test (DFT) and design-for-debug (DFD) facilities, clock tree insertion as well as dynamic power management [16] to ensure the performance

and physical characteristics of the final fabricated chip. Most of these changes are done outside of the design house using untrusted vendors due to time-to-market as well as cost considerations. However, using untrustworthy vendors raise security concerns about the integrity of the design since hardware Trojans can be inserted during changes of the design. In order to trust an IP block, we have to make sure that the IP is performing exactly the expected functionality. Suppose that we have two versions of a design, one is a verified IP (specification) that is designed in-house and the other is an untrusted third-party IP (implementation) after performing non-functional transformations. Our goal is to detect whether an adversary has inserted hard-to-detect hardware Trojan during non-functional changes and has made undesired functional changes. For example, a design house may send their RTL design for synthesis or adding low-power features to a third-party vendor. Once the third-party IP comes back (after synthesis or other functionality-preserving transformations), it is crucial to ensure the trustworthiness of these IPs.

#### 1.1.3 Control Flow Integrity Measurement

The security of an SoC can be compromised by exploiting the vulnerabilities of the nite state machines (FSMs) in the SoC controller modules through fault injection attacks. Fault injection poses a particularly serious threat. During fault attacks, an attacker injects faults to produce erroneous results and then analyzes these results to extract secret information from an SoC [10]. Over the past decade, fault injection attacks have grown from a crypto-engineering curiosity to a systemic adversarial technique [141]. However, most of the research on fault attacks are concentrated on analyzing the fault effects and developing countermeasures for fault injection on datapaths. Finite state machines in the control path are also susceptible to fault injection attacks, and the security of the overall SoC can be compromised if the FSMs controlling the SoC are successfully attacked. For example, it has been shown that the secret key of RSA encryption algorithm can be detected when FSM implementation of the Montgomery

ladder algorithm is attacked using fault injection [129]. Therefore, it is also extremely important to identify and remove FSM vulnerabilities that facilitate fault attacks. These vulnerabilities may be introduced intentionally or unintentionally by designer mistakes, Trojan insertion, and traditional FSM design practices or by CAD tools during synthesis. It has been shown that synthesis tools can introduce security risks in the implemented FSM by inserting additional don't-care states and transitions [44, 102]. Authors in [44] proposed architectural changes in the FSM to address the vulnerabilities introduced by don't-care states and transitions.

#### 1.1.4 Test Generation to Activate Trojans

Untrusted-third party IPs can come with malicious implants. Untrusted EDA tools, in-house rogue employees or the SoC integrator can also insert hard-to-detect Trojans in the original RTL design. We assume that to escape detection during different steps of verification/validation procedure, Trojans are designed in such a way that only a very rare set of input sequences can trigger them. In other words, Trojans are dormant during the normal execution, and activated under unusual (rare) conditions. Therefore, a smart adversary is likely to insert Trojans in RTL designs under rare branches which may reside in the unspecified functionality of the design. Otherwise, traditional simulation techniques using random or constrained-random tests can detect them, and the attacker's attempt would fail. Therefore, we need to have efficient test generation approaches to cover rare branches/assignments in pre-silicon designs in order to activate hidden hardware Trojans.

Post-silicon validation of an integrated circuit (IC) entails running tests on a fabricated, pre-production silicon to ensure that the design functions as expected under actual operating conditions and identify Trojans that have been missed during pre-silicon validation (e.g., RTL or software validation). Post-silicon validation is a highly complex activity, requiring elaborate planning, architectural support, and test development [106]. It is also an expensive activity accounting for more than 50% of the validation cost. Furthermore, post-silicon validation must succeed before mass production can begin.

Thus, effectiveness of post-silicon validation affects product launch, company revenues, profitability, and market positioning [140].

A fundamental problem in post-silicon validation is limited observability and controllability — only a few hundred among the millions of internal signals of an IC can be directly observed or controlled during silicon execution. This makes it difficult to diagnose bugs from observed failures of post-silicon tests, or even identify whether a test has passed, e.g., if the result of a test affects a signal which is not observable. In other words, it is difficult to determine whether the test has executed as expected.

To address this problem, it is critical that post-silicon tests be observability-aware, *i.e.*, produce results whose values can be reconstructed from the available observability. Unfortunately, this is difficult to achieve for several reasons. First, in an industrial IC development environment, observability architecture and (post-silicon) directed tests are developed independently and concurrently by different teams at different points of the design life-cycle. It is often impossible for test generation teams to account for silicon observability since the observability architecture may not have been fully developed at the time of test generation. Furthermore, it is difficult to employ automated tools for creating (additional) observability-friendly directed tests after the observability architecture has been defined. Creating the observability architecture entails analysis of the RTL models to identify traceable signals; these signals are then routed through appropriate hardware instrumentation to an observation point such as an output pin or memory [11, 83, 111]. On the other hand, analysis of RTL models directly to identify test generation is typically infeasible. RTL models tend to be large and complicated (typically millions of lines of code) making such analysis beyond the capacity of test analysis tools. RTL models may also contain functional errors or hardware Trojans. Moreover, there may be Trojans inserted during fabrication via an untrusted manufacturer. Indeed, a key reason for post-silicon directed testing is to identify such Trojans. Consequently, if one develops the directed tests through analysis of the RTL, then the fidelity of the tests as well as any

inference made on their effects on observability, may become questionable. Therefore, it is essential to introduce efficient techniques for observability-aware post-silicon directed generation without utilizing RTL models.

#### 1.1.5 Functional Coverage Analysis of Security Properties

Due to exponential growth of System-on-Chip (SoC) complexity, time-to-market reduction and huge gap between simulation speed and hardware emulation, there is a high chance that many Trojans escape from pre-silicon analysis and it affects the functionality of the manufactured circuit. To ensure the correct operation of the design, post-silicon validation is necessary. However, post-silicon validation is a bottleneck due to limited observability, controllability and technologies to cope with future systems [53, 101]. There is a critical need to develop efficient post-silicon validation techniques.

Currently there is no effective way to collect coverage of certain properties and events such as security properties directly and independently on silicon. Engineers need to assume that they will cover at least the same set of post-silicon coverage events as they cover with pre-silicon exercisers using accelerators/emulators [5]. However, we cannot be sure about the accuracy of these coverage metrics since silicon behaves differently than the simulated/emulated design mainly because of asynchronous interfaces. Moreover, because of time constraints, validation engineers are not able to hit all of the desired coverage events during pre-silicon validation or some coverage events are not activated enough. Therefore, they are seeking for an accurate and efficient way to know the coverage of desired events on silicon.

Assertions and associated checkers are widely used for design coverage analysis in pre-silicon validation to reduce debugging time. They can also be used in the form of coverage monitors to address controllability and observability issues as well as monitoring security events in post-silicon. However, every coverage monitor introduces additional area, power and energy overhead that may violate the design constraints. To address these limitations, there is a need for a framework to reduce the number of coverage monitors in

22

post-silicon while utilize the existing post-silicon infrastructure such as debug facilities to enable functional coverage analysis. In the following section, we describe how these formal methods can be utilized to address the challenges introduced in this section.

#### 1.2 Research Contributions

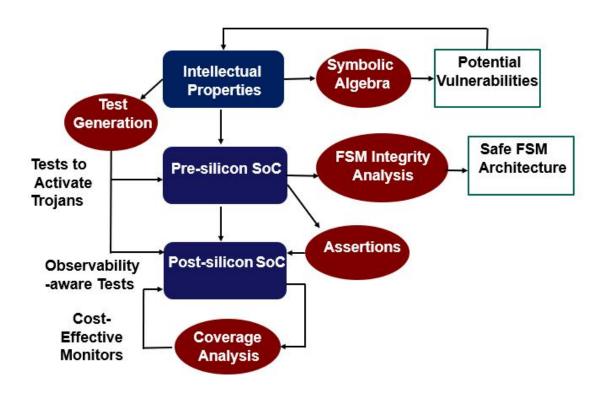

My research proposes novel techniques to address security validation challenges mentioned in Section 1.1. The goal of my research is to introduce efficient algorithms and tools based on formal methods to improve validation efforts at different stages of the design life cycle. Figure 1-4 also illustrates the comprehensive nature of my research that made the following fundamental contributions.

Figure 1-4. Comprehensive nature of my research.

#### Anomaly Detection and Correction in Arithmetic Circuits:

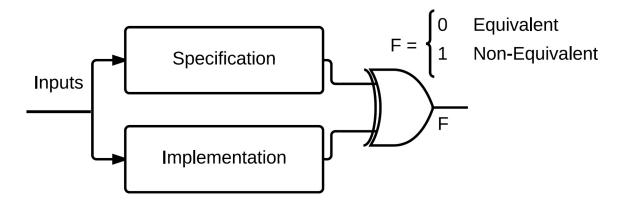

Existing arithmetic circuits verification approaches have focused on checking the equivalence between the specification of a circuit and its implementation. They use an algebraic model of the implementation using a set of polynomials F. The specification of

an arithmetic circuit can be modeled as a polynomial  $f_{spec}$  using a decimal representation of primary inputs and primary outputs. The verification problem is formulated as mathematical manipulation of  $f_{spec}$  over polynomials in F. If the gate-level netlist has correctly implemented the specification, the result of equivalence checking is a zero polynomial; otherwise, it produces a non-zero polynomial containing primary inputs as variables (remainder). In this dissertation, I present a framework for directed test generation and automated debugging of datapath intensive applications using the remainder to detect and correct anomalies in the implementation.

Our method generates directed test vectors that are guaranteed to activate the malfunction. I consider gate misplacement or signal inversion that change the functionality of the design as our threat model. Next, I apply the generated tests, one by one, to find the faulty outputs that are affected by the existing anomaly. Regions that contribute in producing faulty outputs as well as their intersections are utilized for faster error localization. I show that certain errors manifest specific patterns in the remainder. This observation enables an automated debugging to detect and correct the source of error. Existence of a non-zero remainder as a result of applying equivalence checking between specification and implementation of an arithmetic circuit is a sign of a faulty implementation. However, there is no information about the number of existing errors in the implementation. There can be a single bug or multiple independent/dependent bugs in the design. The main question is that how to know the number of remaining bugs in the design and which algorithm should be used to fix them. In order to determine whether there is more than one bug in the implementation, I try to partition the remainder Rinto sub-remainders  $R_i$  first. I detect multiple dependent and independent bugs based on sub-remainders  $R_i$ .

Incremental Anomaly detection Depending on the location of the bug, the remainder generation can be challenging. The existence of a bug in the deeper stages of the design may make it extremely difficult to generate the remainder due to an

explosion in the number of remainder terms (term explosion effect). The reason is that the faulty gate may introduce new terms during the intermediate steps of the specification polynomial's reduction. These extra terms are multiplied to polynomials of other gates and grow continuously until the remainder contains only primary inputs, leading to an explosion in the number of remainder terms.

I also present an incremental equivalence checking approach based on symbolic algebra that is done during several iterations. In each iteration, specification and implementation polynomials are updated based on the primary inputs' constraints, and Gröbner basis reduction is used to generate a remainder in order to define the result of the verification. If the verification results in a non-zero remainder, the implementation is Trojan-inserted. I use the generated remainder as well as inputs' constraints to detect and correct the source of the error. I also show that the order of constraints is important to efficiently debug the faulty implementation. Using the incremental verification approach coupled with different input ordering constraints enable us to efficiently generate remainder for a faulty design.

Trojan Localization using Symbolic Algebra: I propose a design-time formal method to localize and activate Trojans between two versions of a design. Suppose that there is a golden model of a design (specification), and a modified version (implementation) of it (after performing some non-functional changes such as doing synthesis, adding clock trees, scan chain insertion etc.). We would like to make sure that there is no hardware Trojan inserted to the design during the non-functional changes. In other words, our goal is to make sure that two versions of a design are functionally equivalent (nothing more, nothing less) and an adversary cannot hide hard-to-detect malicious modifications during design transformations. It is important to note that traditional equivalence checking techniques can lead to state-space explosion in the presence of specification and implementation of large and complex designs. Our approach

is scalable since it uses polynomial based manipulation instead of Binary Decision Diagrams (BDD [110]).

I propose a formal method based on symbolic algebra to detect potentially malicious modifications in the implementation. Our method is based on extraction of functional polynomial [93] from gate-level IPs.

FSM Integrity Analysis in Controller Design: To detect vulnerabilities introduced by Trojan insertion as well as CAD tools, I propose an efficient, formal analysis framework based on symbolic algebra to find FSM vulnerabilities. The proposed method tries to find inconsistencies between the specification and FSM implementation through manipulation of respective polynomials. Security properties (such as a safe transition to a protected state) are derived using specification polynomials and verified against implementation polynomials. In case of a failure, the vulnerability is reported and a counter-example is generated. While existing methods can verify legal transitions, my approach tries to solve the important and non-trivial problem of detecting illegal accesses to the design states (e.g., protected states). I demonstrate the merit of my proposed method by detecting the vulnerabilities in various current FSM designs, while state-of-the-approaches failed to identify the security flaws.

Trojan Activation by Interleaving Concrete Simulation and Symbolic Execution: I propose a scalable directed test generation method to activate potential hardware Trojans in RTL models. The proposed approach is the

rst attempt in developing an automated and scalable technique to generate directed tests to activate hardware Trojans in RTL models. A threat model involving rare branches and rare assignments is considered in RTL designs. This threat model leads to the automated generation of security assertions. Concolic testing is utilized to generate tests to activate these security assertions. Interleaving concrete simulation with symbolic execution avoids state space explosion by exploring one execution path at a time in contrast to dealing with all possible execution paths at the same time (like conventional

formal methods). Our experimental results demonstrate the effectiveness of our approach in activating hard-to-detect Trojans in large and complex Trust-Hub benchmarks.

Observability-aware Post-Silicon Test Generation: In this dissertation, I present a technique for observability-aware post-silicon directed test generation through analysis of pre-silicon design collaterals. Our key approach to overcome the scalability and relevant challenges mentioned above is to exploit more abstract transaction-level model (TLM) of a design to perform our analysis. TLM definitions are much more abstract, structured, and compact, compared to RTL, which permits effective application of exploration to identify high-quality directed tests. A key challenge is to map design functionality and observability between TLM and RTL so that the tests generated at TLM can be translated to effective, observability-aware tests for RTL. I discuss how to develop this mapping in practice. I provide case studies from a number of different design classes to demonstrate the flexibility and generality of our approach.

Cost-effective Synthesis of Security Assertions: Today's SoCs come with several built-in debug mechanisms such as trace buffers and performance monitors in order to enhance the design observability during post-silicon validation and reduce debugging efforts. Trace buffers record the values of a limited number of selected signals (typically less than 1% of all signals in the design) during silicon execution for specified number of clock cycles. The trace buffer values can be analyzed off-chip to restore the values of untraced signals. I present an approach to utilize the information that can be extracted from on-chip trace buffer in order to determine easy-to-detect functional coverage events using formal analysis. My trace-based coverage analysis enables the trade-off between observability and hardware overhead. The experimental results show that my approach can provide an order-of-magnitude reduction in design overhead without sacrificing functional coverage of security properties compared to when all assertions are synthesized.

#### 1.3 Dissertation Organization

The rest of this dissertation is organized as follows. Chapter 2 discusses the existing security validation approaches. Chapter 3 describes the algebraic preliminaries of formal verification methods based on symbolic algebra and Gröbner basis theory. Gröbner basis theory can be used in hardware Trojan detection as well as integrity analysis of controller designsChapter 4 describes anomaly detection procedure in combinational and arithmetic circuits. In Chapter 5, an incremental debugging approach is presented to improve the required effort for anomaly detection in arithmetic circuits. Chapter 6 introduces a technique for Trojan localization after non-functional changes of the gate-level netlist of the overall design. Chapter 7 describes a technique to identify and mitigate threats in controller designs. Chapter 8 presents a scalable directed test generation method to activate potential hardware Trojans in RTL models. Chapter 9 discusses the observability-aware test generation technique to improve Trojan activation in post-silicon. Chapter 10 presents an approach for getting coverage of post-silicon security properties using post-silicon debug infrastructures. Chapter 11 concludes this dissertation.

# CHAPTER 2 RELATED WORK ON SECURITY VALIDATION

In this chapter, we review the existing security validation methods for SoCs in different stages. There has been plenty of research on trust validation in the IP level, pre-silicon, and post-silicon design. These methods focus on simulation based approaches, side-channel analysis, structural methods as well as formal approaches as shown in Figure 2-1. The remainder of this chapter surveys these approaches in detail.

Figure 2-1. Hardware trust verification can be categorized in three major directions: (1) simulation based approaches, (2) side-channel analysis, and (3) formal approaches.

#### 2.1 Simulation-based Trust Validation Approaches

Simulation-based approaches aim on generating tests to activate malicious modifications (hardware Trojans) and propagate the payload of the Trojan to primary outputs to check with the golden circuit. The difficulty of logic testing is to generate efficient tests to activate and propagate the effect of Trojans, which are stealthy enough to hide through the traditional manufacturing testing.

A major problem with design validation is that we do not know whether a Trojan exists, and how to quickly detect and fix it. We can always keep on generating random

tests, in the hope of activating the Trojan; however, random test generation is neither scalable nor efficient when designs are large and complex.

Several approaches are focused on generation of guided test vectors and compare the produced primary outputs with golden/expected outputs to detect and activate hardware Trojans. Traditional test generation techniques may not be beneficial as Trojans are designed in a way that they will be activated under very rare sequences of the inputs. In this section, we review simulation-based validation approaches including rare-node activation, redundant circuit detection, N-detect ATPG and code coverage techniques.

#### 2.1.1 Functional Test Generation

In a recent case study [144], code coverage analysis and Automatic Test Pattern Generation (ATPG) are employed to identify Trojan-inserted circuits from Trojan-free circuits. The presented method utilizes test vectors to perform formal verification and code coverage analysis in the first step. If this step cannot detect existence of the hardware Trojan, some rules are checked to find unused and redundant circuits. In the next step, the ATPG tool is used to find some patterns to activate the redundant/dormant Trojans. Code coverage analysis is done over RTL (HDL) third party IPs to make sure that there are no hard-to-activate events or corner-case scenarios in the design which may serve as a backdoor of the design and leak the secret information [9, 144]. However, Trojans may exist in design that have 100% code coverage. The MERO (multiple excitation of rare occurrences) approach [30], proposed by Chakraborty et al., can generate high-quality tests to achieve very high activation and coverage rate for Trojans. A later work by Saha et al. [118] extended this approach by using genetic algorithm to further improve the quality of tests. Generating such directed tests is extremely difficult given the stealthiness of activation condition. Besides, this technique is only applicable to gate-level designs and does not guarantee whether the generated tests can activate the Trojans. Cruz et al. have proposed a test generation technique that combines the strength of model checking and ATPG for fast test generation [41]. Their approach partitions the design

based on the scan chain. Constraints are generated for non-scan elements using model checking. These constraints as well as the scan elements are then given to ATPG for test generation. This approach is suitable only for partial scan-chain inserted designs. However, none of the existing techniques are scalable to activate and detect hidden Trojans. Moreover, logic testing would be beneficial when it uses efficient test vectors that can satisfy the Trojan triggering conditions as well as propagate the activation effect to the observable points such as primary outputs. Therefore, the test can reveal the existence of the malicious functionality. These kind of tests are hard to create since trigger conditions are satisfied after long hours of operation and they are usually designed with low probability. As a result, traditional use of existing test generation tools like ATPGs is impractical to produce patterns to activate trigger conditions.

#### 2.1.2 Statistical Methods

Statistical Trojan detection methods try to differentiate the Trojan-inserted circuit from the Trojan-free version using properties of known Trojans. FANCI is one such approach [135]. FANCI marks gates that weakly influence output signals as suspicious. Their proposed algorithm uses approximate truth table for each signal to infer its effect on the outputs. However, FANCI has a high false positive rate. A similar method named VeriTrust marks redundant logic gates as suspicious [142]. Initially, all gates that are not covered during verification phase are considered as suspicious nodes, and further analysis is carried out to confirm redundancy. FANCI and VeriTrust can detect only Trojans with always on or combinational type triggers (a trigger that depends only on current inputs). They cannot detect sequential Trojans, which is exploited by DeTrust benchmarks [143]. Hicks et al. proposed an approach for defeating Trojan based on unused circuit detection [65]. This method relies on the assumption that Trojan circuits will reside on unused portion of the circuit. However, their algorithm failed to detect Trojans that do not rely on unused circuits [125].

A score based classification method for detecting Trojan is discussed in [105]. The classification features are based on properties found from Trojans in Trust-Hub benchmarks [69]. Scores are given to nets for each of the matching features. Nets with score above a threshold are marked as Trojan nodes. Unfortunately, these features are too specific to Trust-Hub benchmarks and thus cannot be used as a generic detection method. A recent approach proposed by Salmani et al. [119] uses SCOAP<sup>1</sup> controllability and observability values to detect and isolate Trojan nodes. Controllability is defined as the number of primary inputs that must be manipulated to control a signal to a particular logic value. Observability is the number of primary input manipulations which is required to make a signal observable at the primary outputs. This method works using the assumption that Trojan nodes will have higher controllability/observability values to avoid detection. However, this approach will result in false positives in designs with partial scan chains. Benign signals that are not part of the scan chain will also have controllability/observability values similar to Trojans. Recently, a Trojan clustering approach based on signal correlation is proposed in [29]. However, this method is suitable for gate-level designs, and cannot be extended to RTL models for early detection.

#### 2.1.3 Side-Channel Analysis

Existing techniques based on side channel analysis rely on the change of physical characteristics caused by the Trojan circuit - mostly in the form of current, power or delay [75, 90, 103]. If the side channel signature of a chip is different from the golden chip over a certain threshold, a Trojan is detected. For example, when a Trojan is partially or fully activated, it will have increased switching activity compared to Trojan free circuit. Wang et al. used this property to isolate Trojan [137]. MERS utilized test generation to improve the Trojan detection sensitivity [74]. Their approach selected the nodes with low transition probability as suspicious nodes. Then test vectors are applied in such a

<sup>&</sup>lt;sup>1</sup> SCOAP: Sandia Controllability/Observability Analysis Program [60]

way that switching activity of these suspicious nodes become much higher than other nodes, increasing side-channel emission. The problem with side channel analysis is the presence of process variation and measurement noise. Side-channel based approaches face difficulty if the Trojan circuit is small. This is because difference in side channel signature due to the Trojan can be negligible compared to process variations. These methods also require Trojan free golden reference models. As side-channel analysis is carried out after fabrication, the chip may require re-spins if Trojan is detected. Thus, methods that can detect Trojan in an early design stage is highly desirable.

#### 2.2 Security validation using Formal methods

Formal methods are promising in hardware validation as they evaluate the functionality and structure of the mathematical model to verify that the design correctly implements the functions described in the specification. Formal verification methods can be broadly classified in four groups: i) Satisfiability (SAT) solvers, ii) property checking using model checkers [19, 99], iii) theorem proving approaches [42], and iv) equivalence checking using decision graphs [25, 35, 110] and symbolic algebra [49]. In this section, we briefly discuss each of these methods and their applications for security validation. We focus on different formal methods to verify the design and detect un-desired functions (possibly Trojans).

#### 2.2.1 Trust Validation using SAT Solvers