# **DUO-Dual TCAM Architecture for Routing Tables with Incremental Update** \*

Tania Mishra and Sartaj Sahni

Department of Computer and Information Science and Engineering,

University of Florida, Gainesville, FL 32611

{tmishra, sahni}@cise.ufl.edu

### **Abstract**

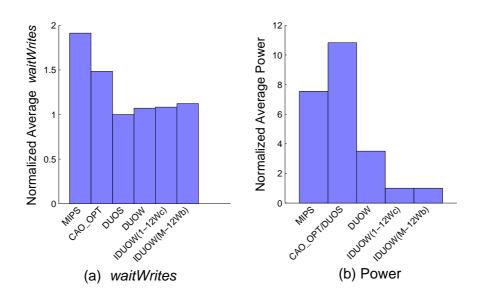

We propose a dual TCAM architecture-DUO- for routing tables. Four memory management schemes for TCAMs also are proposed and evaluated. DUO and our memory management schemes support control-plane incremental updates without delaying data-plane lookups. Compared to other TCAM architectures such as CAO\_OPT [23] that support incremental updates without delaying lookups, DUO offers reduction in power consumption and/or improvement in worst-case performance for update operations.

### **Keywords**

IP routing table, consistent lookup, incremental updates, power.

### 1 Introduction

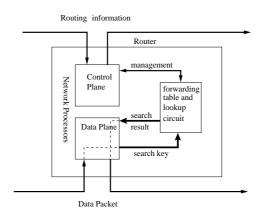

The primary function of an Internet router is to forward packets using a table of rules. A packet forwarding rule (P, H) comprises a prefix P and a next hop H. A packet with destination address d is forwarded to H where H is the next hop associated with the rule that has the longest prefix that matches d. We refer to the set of rules as the rule table or forwarding table. Packet forwarding is performed in the data plane while route updates are done in the control plane. Whereas the data plane receives tens or even hundreds of millions of packets per second, the control plane receives only thousands of update requests per second. Figure 1 illustrates the high level functions of control and data planes.

Figure 1. Control and Data Planes in Routers

With the rapid global spread of the Internet, the forwarding table size at each router is growing fast as is the number of route updates that are received by a router due to extensive interconnections. Presently, the largest forwarding tables have about one million rules and the number of updates peaks at about 10,000 updates per second. At a line rate of 10Gbps and a minimum packet size of 40 bytes, the number of data plane lookups per second exceeds 30 million.

<sup>\*</sup>This research was supported, in part, by the National Science Foundation, under grant 0829916.

A number of fast lookup schemes have been proposed in literature that use TCAMs as the main hardware component, because TCAMs are simple to use and provide high-speed table lookup [12, 13] ([12, 13] also survey non-TCAM approaches to routing table management). A TCAM is a special type of content addressable memory (CAM) that allows each memory bit to store one of the three values: 0, 1, x (don't care). The prefix of a rule is stored in a word of TCAM and the next hop is stored in the corresponding word of an associated SRAM. The entries of a TCAM may be searched in parallel for a prefix that matches a given destination address. If multiple matching entries are found then the best match is selected by a priority encoder. The best match is quite frequently identified as the first entry that matches. Using the index of the best matched TCAM entry, we access the corresponding SRAM word to determine the next hop. When the prefixes are stored in decreasing order of prefix length, it is possible to determine the TCAM index of the longest matching prefix for any destination address in one TCAM cycle. We note that, a TCAM word will be 32 bits for IPv4 applications. The described TCAM scheme is referred to as the *simple TCAM scheme* [4].

The main drawback of using TCAMs in a router's forwarding engine is that a TCAM consumes a high amount of power for each lookup operation since every TCAM cell in the array is activated for each lookup. There has been a significant amount of research in trying to reduce the power consumption in TCAMs [4, 18, 19, 23, 21, 22]. Lu and Sahni in [4] propose a technique that utilizes wide SRAMs to store portions of prefixes along with their next hops in each SRAM word. This scheme reduces the TCAM size and power requirement drastically. The Simple TCAM with Wide SRAM (STW) organization is the basic scheme in [4] that demonstrates the potential of saving TCAM space and power by utilizing wide SRAM words. One drawback of the STW scheme is that incremental update algorithms are complex because of the need to handle covering prefixes that may be replicated many times. On the other hand, batch update algorithms require twice the memory footprint so forwarding and updating can be applied on two separate copies of the forwarding table [22].

Wang et al. [18] propose a consistent table update scheme that eliminates the need to lock the forwarding table during an update, preserving the correctness of rule matching at all times. Since lookups can proceed at their usual speed even as updates are being carried out, there is no need to minimize the number of rule moves required to incorporate an update as long as the rate of processing keeps up with the arrival rate for updates. However, this does not undermine the advantage of a fast update process requiring a smaller number of rule moves since with a faster process fewer packets will be forwarded to non-optimal next hops.

Wang and Tzeng [19] use leaf pushing to transform the prefixes in the routing table into a set of independent prefixes, which are then stored in a TCAM (in any order). Their consistent update scheme, however, delays data plane lookups that match TCAM slots whose next hop information is being updated. Although, on average, each insert or delete request results in a very small number of insert/delete operations on the set of independent prefixes stored in the TCAM, worst-case inserts and deletes require  $\Omega(n)$  insert/delete operations on the set of independent prefixes, where n is the number of independent prefixes. Hence, an adversary can significantly compromise the router by maliciously injecting a sequence of worst-case updates. Further, the method of [19] uses a TCAM search to find a free TCAM slot for an insert and this search interrupts the lookups taking place in the data plane.

In this paper we present three versions of our novel dual TCAM architecture, generally referred to as DUO, along with advanced memory management schemes for performing efficient and consistent incremental updates without degrading lookup speed. The first version of the architecture is DUOS – dual TCAM with simple SRAM, where both the TCAMs have a simple associated SRAM that is used for storing next hops. The second version of the architecture is DUOW – dual TCAM with wide SRAM, where one or both the TCAMs have wide associated SRAMs that are used to store suffixes as well as next hops. The third version is IDUOW – indexed dual TCAM with wide SRAM, in which either or both TCAMs have an associated index TCAM. The advantages of the dual TCAM architecture and the memory management schemes presented in this paper are:

1. Like the TCAM schemes CAO\_OPT [23] and MIPS [19], DUO supports incremental updates. This means that we may do updates on the forwarding table one by one efficiently in DUO. In particular, DUO allows us to do an update with no slow down in data plane lookups. In contrast, TCAM schemes such as those of [4, 21] support batch updates only. These latter schemes employ two TCAMs. At any time, one of these is active and the other inactive. The active TCAM is used for data plane lookups. Updates are accumulated, in the control plane, as they arrive over a pre-specified interval. At the end of each accumulation period, the control plane constructs a new forwarding

table in the inactive TCAM. Note that during this construction process that takes place in the control plane, data plane lookups are unaffected as these use the active TCAM. Following the construction of the forwarding table in the inactive TCAM, the roles of active and inactive TCAMs are switched incurring minimal data plane lookup delay. As can be seen, batch schemes require twice the TCAM memory required by incremental schemes and have a significantly larger latency between the arrival of an update request and the time this update is incorporated into the active forwarding table.

- 2. Incremental updates in DUOS require far fewer rule moves than required by the simple TCAM scheme. The total TCAM and SRAM space used by DUOS is the same as that used by the simple TCAM scheme.

- 3. The wide SRAM scheme of [4], which is a batch scheme, may be coupled with DUOS to arrive at DUOW and IDUOW, which provide considerable reduction in TCAM memory and power while preserving the efficient incremental update capability of DUOS.

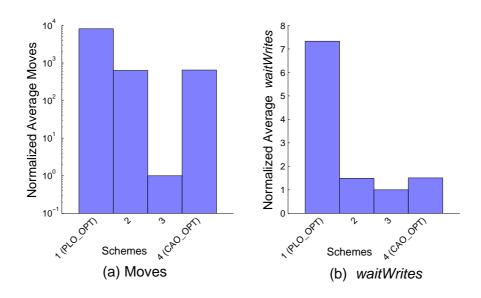

- 4. Employing memory management scheme DLFS\_PLO (Scheme 3) to manage the memory of a simple TCAM enables the simple TCAM to outperform the CAO\_OPT scheme (Scheme 4) of [23] with respect to the time required to complete update sequences that arise in practice. Compared to the PLO\_OPT memory management scheme (Scheme 1) proposed in [23], however, CAO\_OPT is superior (as expected by the analysis of [23]).

The rest of the paper is organized as follows. Section 2 presents related research work. The DUOS architecture and our memory management schemes are described in Section 3, DUOW is described in Section 4, and IDUOW is described in Section 5. An experimental evaluation of DUO is presented in Section 6 and we conclude in Section 7.

### 2 Background and Related Work

The high-speed table lookup property of TCAMs is a key feature for implementation of fast engines to be used in packet forwarding. Research on TCAM routers has focused on lowering the power consumption [11, 8, 4, 9, 10, 2, 22, 21, 15, 14, 16, 17], creating new router architectures involving multiple TCAMs that achieve even faster lookup [27, 26], and developing efficient strategies for incremental updates [23, 18, 19]. Since our focus in this paper is to develop router architectures that have efficient support for incremental updates, we present work related to TCAM incremental updates in some detail.

Shah and Gupta [23] describe incremental update algorithms for TCAMs using two different strategies to place prefixes in the TCAM. In PLO\_OPT, the prefixes are placed in the TCAM in decreasing order of length. Unused TCAM slots/words are in the middle of the TCAM. So, prefixes of length  $W, \cdots, W/2+1$  are above the free slots and the remaining prefixes are below the free slots, where W=32 for IPv4. An insert or delete requires at most W/2 prefix moves in PLO\_OPT. In CAO\_OPT, the prefixes are placed in the TCAM so that if two prefixes are nested, the longer prefix precedes the shorter one. If we start with the binary trie representation of the prefixes of the routing table, the prefixes along any path from the trie root to a trie leaf are nested. So, every root to leaf path in the trie defines a chain of nested prefixes. In CAO\_OPT, the prefixes on every chain appear in reverse order in the TCAM. This placement ensures that the first prefix in the TCAM that matches a destination address is the longest matching prefix. The TCAM free slots are in the middle of the TCAM. If the maximum number of prefixes in a nested chain is q, then at most  $\lceil q/2 \rceil$  prefixes of a chain are above the free slots. An insert or delete in CAO\_OPT requires at most  $\lceil q/2 \rceil = W/2$  moves. Since q is about 6 in practical routing tables, CAO\_OPT gives a performance improvement over PLO\_OPT in practice (though the worst-case performance of both is the same).

Wang et al. [18] define a *consistent rule table* to be a rule table in which the rule matched (including the action associated with the rule) by a look up operation performed in the data plane is either the rule (including action) that would be matched just before or just after any ongoing update operation in the control plane. Wang et al. [18] develop a scheme for consistent table update without locking the TCAM at any time, essentially allowing a search to proceed while the table is being updated. Consistency is ensured by avoiding overwriting of a TCAM entry. Their CoPTUA algorithm can be applied to the PLO\_OPT and CAO\_OPT schemes of [23] so that rule updates can be carried out without locking the table for data plane lookups under suitable assumptions for TCAM operation [18].

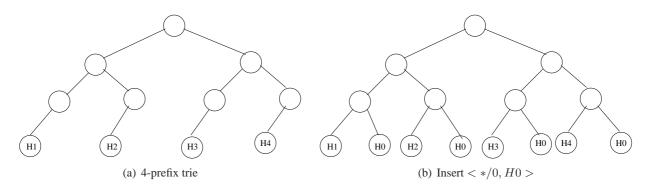

Wang and Tzeng [19] also propose a consistent TCAM scheme. Their scheme, MIPS, however delays data plane lookups that match TCAM slots whose next hop information is being updated. In MIPS, the TCAM stores a set of independent prefixes (i.e., disjoint). This set of independent prefixes is obtained from the original set of prefixes by using the leaf pushing technique [25] followed by a compression step. Since the prefixes in the TCAM are independent, at most one prefix matches any given destination address. Hence, the independent prefixes may be placed in the TCAM in any order and we may dispense with the priority encoder logic of the TCAM, which results in a reduction in TCAM lookup latency by about 50% [24]. Further, a new prefix may be inserted into any free slot of the TCAM and an old prefix deleted by simply setting the associated slot's *valid* bit to 0. While the use of an independent prefix set simplifies table management, leaf pushing replicates a prefix many times. In the worst case, an insert or delete, requires changes to  $\Omega(n)$  TCAM entries, where n the number of independent prefixes in the TCAM (Figure 2). Furthermore, the number of independent prefixes that result from leaf pushing and compression can be quite large as, in the worst-case, the compression step may fail to do any reduction in the prefix set following leaf pushing. Experimental results presented in [19] suggest, however, that, on practical rule sets, leaf expansion and compression actually reduce the number of prefixes by 20% to 68% because of the prevalence of a large number of redundant prefixes in practical rule sets. Further, each update operation results in between one and two accesses to the TCAM on average. Wang and Zheng [19] do not use any memory management scheme to keep track of the free slots in the TCAM and instead rely on a TCAM search operation to find an empty slot when such a slot is needed. Since a TCAM cannot perform a data plane search concurrent with a control plane search, update operations delay data plane lookups. In practice, since the number of updates per second is quite small and since each routing table update results in only one or two TCAM update operations (on average) the delay caused by control plane lookups on data plane lookups is quite small. As TCAM lookups consume a significant amount of energy relative to that consumed by TCAM read/write operations, using lookups to locate free TCAM slots increases total energy consumption for updates significantly.

Figure 2. Insertion of the root prefix into (a) requires the insertion of 4 new independent prefixes into the TCAM. Similarly, the deletion of the root prefix from (b) requires the withdrawal of these 4 prefixes from the TCAM

Zane et al. [21] propose an indexed TCAM scheme to reduce the total TCAM power used to search routing tables of a given size. The indexed TCAM schemes of [21], however, increase the total TCAM size needed relative to non-indexed TCAMs. Lu and Sahni [4] couple indexed TCAMs with wide SRAMs to reduce both power and TCAM memory by a significant amount. Although the strategies of [4] are power and memory efficient, they are not well suited to incremental update. Similarly the prefix compaction methods of [11, 8, 22], while resulting in power and memory reduction, do not lend themselves well to incremental update. Chang [2] proposes a TCAM partitioning and indexing scheme in which the TCAM index is stored in a pivot prefix SRAM and an index SRAM. In Chang's scheme [2], the TCAM index is searched using a binary search that makes  $O(\log K)$  SRAM accesses to determine the TCAM bucket that is to be searched. On the other hand, the scheme of Zane et al. [21] stores its index in a TCAM enabling the determination of the bucket for further search by a query on the index TCAM. As a result, a lookup takes 2 TCAM searches when the scheme of [21] is used and take 1 TCAM search plus  $O(\log K)$  SRAM accesses when the scheme of [2] is used.

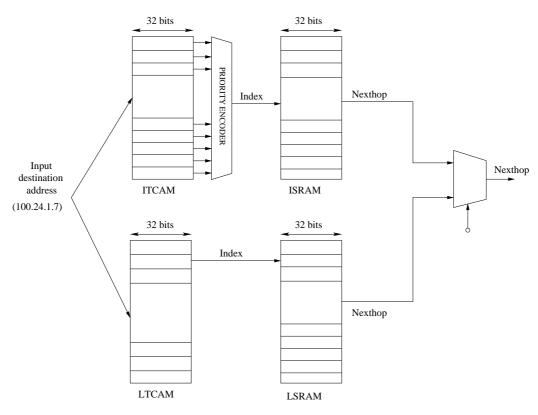

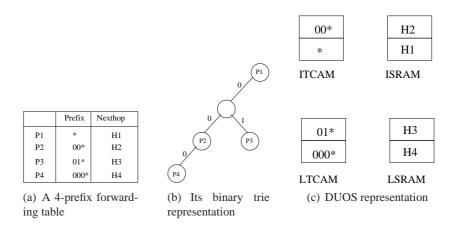

### 3 Simple Dual TCAM – DUOS

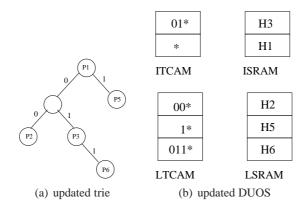

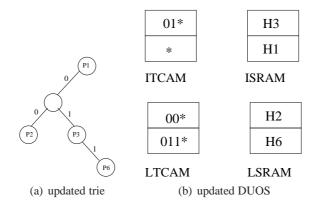

DUOS uses any reasonably efficient data structure to store the routing-table rules in the control plane. For example, a simple data structure such as a binary trie or 1-bit trie stored in a 100ns DRAM, permits about 300K IPv4 lookups, inserts, and deletes per second. This performance is quite adequate for the anticipated tens of thousands of control plane operations. For concreteness, we assume that a binary trie is used, in the control plane, to store the routing-table rules. Additionally, DUOS uses two TCAMs each with an associated SRAM. The TCAMs are labeled ITCAM (Interior TCAM) and LTCAM (Leaf TCAM) in Figure 3. The associated SRAMs are similarly labeled. Prefixes stored in leaf (non leaf or interior) nodes of the control plane trie are stored also in the LTCAM (ITCAM) and their associated next hops are stored in the LSRAM (ISRAM). Since the LTCAM stores only leaf prefixes, the prefixes in the LTCAM are disjoint and at most one may match a given destination address. Consequently, the LTCAM prefixes, even though of varying length, may be stored in any order. Further, the LTCAM does not require a priority encoder and, as a result, the latency of an LTCAM search is up to 50% less than that of a search in a TCAM with a priority encoder [28]. A data plane lookup is performed by doing a search for the packet's destination address in both ITCAM and LTCAM. The ITCAM search yields the next hop associated with the longest matching non-leaf prefix while the LTCAM search yields the next hop associated with at most one leaf prefix that matches the destination address. Additional logic shown in Figure 3 returns the next hop (if any) from the LTCAM search; the next hop from the ITCAM search is returned only if the LTCAM search found no match. Note that since the LTCAM has no priority encoder, its search completes sooner than that in the ITCAM. The combining logic of Figure 3 can take advantage of this and abort the ITCAM search whenever the LTCAM search is successful, thereby reducing average lookup time. The correctness of the lookup is readily established. Figure 4 shows a 4-prefix

Figure 3. Dual TCAM with simple SRAM

forwarding table together with its corresponding binary trie that is stored in the control plane as well as the content of the two TCAMs and the two SRAMs of DUOS.

Each node of the control plane trie has fields such as *prefix*, *slot*, *nexthop* and *length* in which the prefix (if any) stored at this node is recorded along with the ITCAM or LTCAM slot in which the prefix is stored and the nexthop and length

Figure 4. DUOS for an example 4-prefix forwarding table. Note that prefixes in ITCAM are stored in length order, whereas those in LTCAM are stored arbitrarily since the prefixes are disjoint.

of the prefix. Functions for basic operations on the control plane trie (hereinafter simply referred to as trie) are assumed (see Figure 5).

# **Function:** Trie.insert

(a, b) = Trie.insert(prefix, length, nextHop);

This function inserts a prefix given its length and next hop into the control-plane binary trie. It returns the trie node a which stores the new prefix and a's nearest ancestor node b that contains a prefix.

### **Function: Trie.delete**

(a, b) = Trie.delete(prefix, length);

This function deletes a prefix from the control plane trie and returns the trie node a that used to store the prefix just deleted and a's nearest ancestor node b that contains a prefix.

### **Function: Trie.change**

a = Trie.change(prefix, length, newHop);

This function changes the next hop associated with a prefix and returns the trie node a that contains the prefix.

Figure 5. Table of control-plane trie functions

As the control plane will modify the ITCAM, LTCAM, ISRAM, and LSRAM while the data plane performs lookups, the TCAMs need to be dual ported. Specifically, we make the following assumptions:

- 1. Each TCAM has two ports, which can be used to simultaneously access the TCAM from the control plane and the data plane.

- 2. Each TCAM entry/slot is tagged with a valid bit, that is set to 1 if the content for the entry is valid, and to 0 otherwise. A TCAM lookup engages only those slots whose valid bit is 1. The TCAM slots engaged in a lookup are determined at the start of a lookup to be those slots whose valid bits are 1 at that time. Changing a valid bit from 1 to 0 during a data plane lookup does not disengage that slot from the ongoing lookup. Similarly, changing a valid bit from 0 to 1 during a data plane lookup does not engage that slot until the next lookup.

We assume the availability of the function waitWriteValidate which writes to a TCAM slot and sets the valid bit to 1. In case the TCAM slot being written to is the subject of ongoing data plane lookup, the write is delayed till this lookup

completes. During the write, the TCAM slot being written to is excluded from data plane lookups<sup>1</sup>. This is equivalent to the requirement that "After a rule is matched, resetting the valid bit has no effect on the action return process" [18], and to setting the valid entry to "hit" [19]. Similarly, we assume the availability of the function invalidateWaitWrite, which sets the valid bit of a TCAM slot to 0 and then writes an address to the associated SRAM word in such a way that the outcome of the ongoing lookup is unaffected.

We note that waitWriteValidate may, at times, write the prefix and nexthop information in the TCAM and associated SRAM slot and validate it, without any wait. This happens, for example, when the writing is to be done to a TCAM slot that is not the subject of the ongoing data plane lookup. The wait component of the function waitWriteValidate is said to be null in this case.

Figure 6 lists the various update algorithms we define later in this section for DUOS and its associated ITCAM and LTCAM. The indentation represents the hierarchy of function calls. A function at one level of indentation calls one or more functions below it at the next level of indentation or at the same level of indentation.

```

dual-TCAM:

insert

delete

change

ITCAM (with simple SRAM):

insert

delete

change

getSpace

freeSpace

movesFromAbove

movesFromBelow

getFromAbove

getFromBelow

LTCAM (with simple SRAM)

insert

delete

change

LTCAM (with wide SRAM)

insert

delete

change

addSuffix

split

carve

```

Figure 6. Table of functions used for incremental update

### 3.1 DUOS Incremental Update Algorithms

### **3.1.1** Insert

Figure 7 gives the algorithm to insert a new prefix p of length l and nexthop h. For simplicity, we assume that p is, in fact new (i.e., p is not already in the rule table). First, p is inserted into the trie using the trie insertion algorithm, which returns nodes m and n, where m is the trie node storing p and n is the nearest ancestor (if any) of m that has a prefix. When m is a leaf of the trie, there is a possibility that the insertion of p transformed a prefix that was previously a leaf prefix into a non-leaf prefix. If so, this prefix is moved from the LTCAM to the ITCAM. Regardless, p is inserted into

<sup>&</sup>lt;sup>1</sup>A possible mechanism to accomplish this exclusion is to set the valid bit to 0 before commencing the write and to change this bit to 1 when the write completes.

```

Algorithm: insert (p, l, h)

(m, n) = \text{Trie.insert}(p, l, h)

if m is a leaf then begin

if n exists and n \rightarrow prefix was a leaf prefix then

slot = \text{ITCAM.insert}(n \rightarrow prefix, n \rightarrow nexthop, n \rightarrow length); // n \rightarrow prefix is no longer a leaf

LTCAM.delete(n \rightarrow slot);

n \rightarrow slot = slot;

endif

m \rightarrow slot = \text{LTCAM.insert}(p, h, l);

else m \rightarrow slot = \text{ITCAM.insert}(p, h, l);

endif

```

Figure 7. Algorithm to insert into DUOS

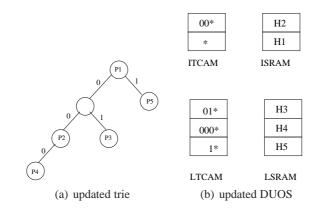

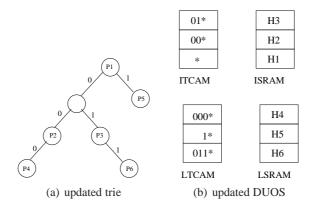

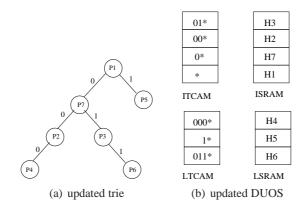

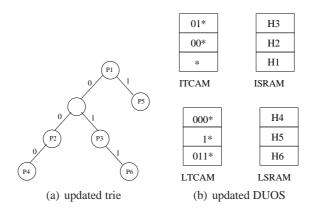

the LTCAM. When m is not a leaf, p is inserted into the ITCAM. Figure 8, 9 and 10 illustrate the insertion of rules P5, P6 and P7 respectively starting with the initial prefix trie in Figure 4.

Figure 8. Insert rule P5 - {1\*, H5} to the initial table in Figure 4. P5 is a leaf and hence is added to the LTCAM

### **3.1.2** Delete

Figure 11 gives the algorithm to delete the prefix p from DUOS. For simplicity, we assume that p is, in fact, present in the rule table and so may be deleted. First, p is deleted from the trie. The trie deletion function returns nodes m and n, where m is the trie node where p was stored and n is the nearest ancestor (if any) of m that has a prefix. If m was a leaf, then p is to be deleted from the LTCAM. In this case, the prefix (if any) in n may become a leaf prefix. If so, the prefix in n is to be moved from the ITCAM to the LTCAM. When m is not a leaf, p is deleted from the ITCAM. Figure 12, 13 14 illustrate the delete procedure of prefixes P7, P4 and P5 respectively starting with the prefix trie in Figure 10.

### **3.1.3** Change

To change the nexthop of an existing prefix to newH, we first change the next hop of the prefix in the trie and return the node m that contains p. Then, depending on whether m is a leaf or non leaf, we invoke the change function for the corresponding TCAM. Figure 15 gives the algorithm.

Figure 9. Insert rule P6 -  $\{011^*, H6\}$  to the prefixes in Figure 8. P6 is added to the LTCAM, while P3, which is no longer a leaf, is deleted from LTCAM and added to ITCAM.

Figure 10. Insert rule P7 -  $\{0^*, H7\}$  to the prefixes in Figure 9. P7 is added to the ITCAM since it involves an intermediate prefix.

Figure 11. Algorithm to delete from DUOS

Figure 12. Delete rule P7 - {0\*, H7} from the prefixes in Figure 10. P7 is deleted from ITCAM.

Figure 13. Delete rule P4 - {000\*, H4} from the prefixes in Figure 12. P4 is deleted from LTCAM. P2 is inserted to LTCAM and deleted from ITCAM as P2 is now a leaf.

Figure 14. Delete rule P5 - {1\*, H5} from the prefixes in Figure 13. P5 is deleted from LTCAM.

```

Algorithm: change (p, length, newH)

m = \text{Trie.change}(p, l, newH)

If m is a leaf then

m \rightarrow slot = \text{LTCAM.change}(p, m \rightarrow slot, newH);

else

m \rightarrow slot = \text{ITCAM.change}(p, m \rightarrow slot, newH, length);

```

Figure 15. Algorithm to change a next hop in DUOS

### Algorithm: insert(prefix, nexthop, length)

```

slot = getSlot(length);

ITCAM.waitWriteValidate(slot, prefix, nexthop);

return slot;

```

### Algorithm: delete(slot, length)

freeSlot(slot, length);

### Algorithm: change(prefix, oldSlot, nexthop, length)

```

slot = insert(prefix, nexthop, length);

delete(oldSlot, length);

return slot;

```

Figure 16. ITCAM algorithms

### 3.2 ITCAM Algorithms

The prefixes in the ITCAM are stored in such a manner as to support determining the longest matching prefix (i.e., in any topological order that conforms to the precedence constraints defined by the binary trie-p1 must come before p2 whenever p1 is a descendent of p2 [23]). Decreasing order of length is a commonly used ordering. The function getSlot(length) returns an ITCAM slot such that insertion of the new prefix into this slot satisfies the ordering constraint in use provided the new prefix has the specified length; the function freeSlot(slot, length) frees a slot previously occupied by a prefix of the specified length and makes this slot available for reuse later. These functions, which are described in Section 3.4, are used in our ITCAM insert, delete, and change algorithms (Figure 16), which are self explanatory.

Notice that following the first step of the change algorithm, the prefix whose next hop is being changed is in two valid slots of the ITCAM–oldSlot and slot. This duplication does not affect correctness of data plane lookups as whichever one is matched by the ITCAM, we return the next hop that is valid either before or after the change operation. On the other hand, if we attempted to change the next hop in ISRAM[oldSlot] directly, an ongoing lookup may return a garbled next hop. Similarly, if we delete first and then insert, lookups that take place between the delete and the insert may return a next hop that doesn't correspond to the routing table state either before or after the change. If a waitWriteValidate is used to change ISRAM[oldSlot] to nexthop, oldSlot becomes unavailable for data plane lookups during the write operation and inconsistent results are returned in case the prefix in TCAM[oldSlot] is the longest matching prefix.

### 3.3 LTCAM Algorithms

The prefixes in the LTCAM are disjoint and so may be stored in any order. The unused (or free) slots of the LT-CAM/LSRAM are linked together into a chain using the words of the LSRAM to build this chain. We use AV to store the index of the first LSRAM word on the chain. So, the free slots are AV, LSRAM[AV], LSRAM[LSRAM[AV]], and so on. The last free slot on the AV chain has LSRAM[last] = -1. The LTCAM algorithms to insert, delete, and change are given in Figure 17. These algorithms are self explanatory.

# 3.4 ITCAM Memory Management

In this section, we describe four possible memory management schemes for an ITCAM. The description of each memory management scheme includes an implementation of the *getSlot* and *freeSlot* functions used in Section 3.2 to get and free ITCAM slots. The implementations employ the function *move* (Figure 18) that moves the content of an in-use ITCAM slot to a free ITCAM slot in such a way as to maintain data plane lookup consistency. Our memory

```

Algorithm: insert(prefix, nexthop, length)

if (AV == -1) throw NoSlotException;

slot = AV;

AV = LSRAM[slot];

LTCAM.waitWriteValidate(slot, prefix, nexthop);

return slot;

Algorithm: delete(slot)

LTCAM.invalidateWaitWrite(slot, AV); // AV is stored in LSRAM[slot] after waiting

/// for an ongoing lookup to complete

AV = slot;

Algorithm: change(prefix, oldSlot, nexthop, length)

slot = insert(prefix, nexthop, length);

delete (oldSlot);

return slot;

```

Figure 17. LTCAM algorithms

```

Algorithm: move (src, dest)

ITCAM.waitWriteValidate(dest, ITCAM[src], ISRAM[src]);

```

Figure 18. Move from ITCAM[src] to ITCAM[dest]

management algorithms maintain the invariant that an ITCAM slot has its valid bit set to 0 iff that slot wasn't matched by the ongoing data plane lookup (if any); that is, iff the slot isn't involved in the ongoing data plane lookup.

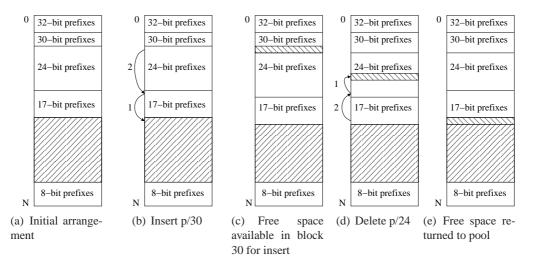

### 3.4.1 Memory Management Scheme 1

This scheme, which is the PLO\_OPT scheme of [23], is shown in Figure 19(a), the ITCAM slots are indexed 0 through N. The prefixes are stored in decreasing order of length in the TCAM, which ensures that the longest matching prefix is returned as the first matching prefix. The pool of free slots is kept at the logical center of the TCAM, that is, the first free slot in the pool appears after all blocks of prefixes of length W/2+1 or more and the last free slot appears before all blocks of prefixes of length W/2 or less, where W is the width of the IP address (32 in the case of IPv4). As noted in [23], this scheme requires at most W/2 moves for each getSlot and freeSlot request. Our contribution is to provide an implementation that maintains consistency of data plane lookups.

```

Our lookup consistent implementation of getSlot and freeSlot employ the following variables: W = \text{prefix length} \ (32 \text{ for IPv4}) top[i] = \text{first slot used by block } i, \ 1 \le i \le W/2 bot[i] = \text{last slot used by block } i, \ W/2 + 1 \le i \le W

The following invariants are maintained:

```

```

top[i] = top[i-1] iff block i is empty, 1 \le i \le W/2

bot[i] = bot[i+1] iff block i is empty, W/2 + 1 \le i \le W

```

Initially, all blocks are empty and top[0: W/2] = N+1 and bot[W/2+1: W+1] = -1 (recall that the ITCAM slots are indexed 0:N). Figures 20 and 21, respectively, give the getSlot and freeSlot algorithms for Scheme 1. Their correctness and the fact that data plane lookup consistency is preserved are easily established.

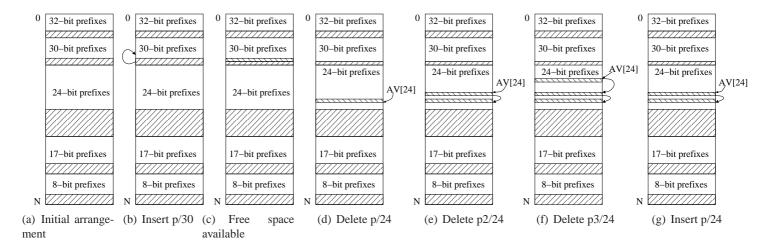

Figure 19. Prefix arrangement in ITCAM for Scheme 1 for IPv4. The free space pool is indicated by hatched lines. Numbers 1, 2 by the curved arrow correspond to the first and second move, respectively.

### 3.4.2 Memory Management Scheme 2

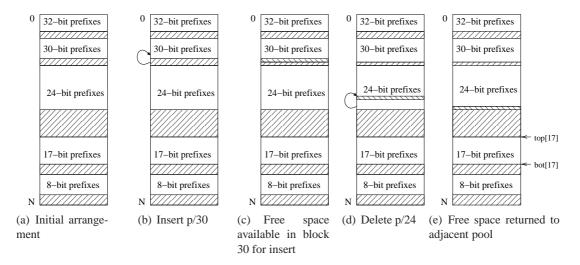

This scheme is a variation of Scheme 1 in which the free slots are in the boundary between two prefix blocks (Figure 22). This scheme is also called DFS\_PLO (Distributed Free Space with Prefix Length Ordering Constraint). At the time the ITCAM is initialized, the available free slots are distributed in proportion to the number of prefixes in a block with the caveat that an empty block gets 1 free slot at its boundary. In this scheme, top[i] is the slot where the first prefix of length i is stored and top[i] is the slot where the last prefix of length i is stored,  $0 \le i \le W$  (i.e., these variables define the start and end of block i). Note that  $top[i] \le bot[i]$  for a non-empty block i and top[i] > bot[i] for an empty block. For convenience, we define top[0]=bot[0]=N+1 and top[W+1]=bot[W+1]=-1. For an empty ITCAM, top[i]=N+1 for  $1 \le i \le W$ ; tot[i]=-1 for  $1 \le i \le W$ .

Our getSlot algorithm (Figure 23) provides a free slot from either block boundary when there is a free slot on the block boundary. Otherwise, it moves a free slot from the nearest block boundary that has a free slot. This algorithm utilizes several supporting algorithms that are given in Figure 24. The algorithm  $movesFromAbove\ (movesFromBelow)$  returns the number of prefix moves that are required to get the nearest free slot from above (below) the block where it is needed and getFromAbove and getFromBelow, respectively, get the nearest free slot above or below the block where the free slot is needed.

The algorithm to free a slot (Figure 25) simply moves the slot to be freed to the block boundary unless this slot is at the boundary to begin with. Again, correctness and consistency are established easily. Although the worst-case performance of the Scheme 2 algorithms is the same as that of the Scheme 1 algorithms, we expect the Scheme 2 algorithms to have better performance on average.

### 3.4.3 Memory Management Scheme 3

This is an enhancement of Scheme 2 in which we maintain a doubly-linked list of free slots within each block in addition to contiguous free slots at the block boundaries (Figure 26). This scheme is also called DLFS\_PLO (Distributed and Linked Free Space with Prefix Length Ordering Constraint). The lists of free slots within a block enable us to avoid the move that is done by the Scheme 2 *freeSlot* algorithm of Figure 25. The forward links, called next[], of the doubly-linked list are maintained using the ISRAM words corresponding to the free ITCAM slots with AV[i] recording the first slot on the list for the ith block. The backward links, called prev[], are maintained in these ISRAM words in case an ISRAM word is large enough to accommodate two links and in the control plane memory otherwise. All variables, including the array AV[], are, of course, stored in the control plane memory.

```

Algorithm: getSlot(len)

//len: length of prefix to be inserted.

// returns free slot for prefix insertion

if (bot[W/2 + 1] == top[W/2] - 1) throw NoSpaceException;

if (len \ge W/2 + 1)

d = ++bot[W/2 + 1];

for (i = W/2 + 2; i \le len; ++i)

if (bot[i] == d-1) // block i - 1 is empty

bot[i] = bot[i-1];

else // move from top of i-1 to d

s = ++bot[i];

move(s, d);

d = s;

endif

else

d = -\text{top}[W/2];

for (i = W/2 - 1; i >= len; - - i)

if (top[i] == d+1) // block i + 1 is empty

top[i] = top[i+1];

else // move from bottom of i+1 to d

s = --top[i];

move(s, d);

d = s;

endif

endif

```

Figure 20. Scheme 1 algorithm to get a free slot to insert a prefix whose length is len

```

Algorithm: freeSlot(slot, len)

// free ITCAM[slot] which had a prefix of length len

if (len \ge W/2 + 1) // free space from the top half.

if (slot != bot[len])

move (bot[len], slot); slot = bot[<math>len];

endif

bot[len]--;

for (i = len - 1; i > W/2; - -i)

if (bot[i] != slot) // block i is not empty

move (bot[i], slot); slot = bot[<math>i];

endif

bot[i]--;

endfor

else // free space from the bottom half.

if (slot != top[len])

move (top[len], slot); slot = top[len];

endif

top[len]++;

for (i=len+1; i \le W/2; ++i)

if (top[i] != slot) // block i is not empty

move (top[i], slot); slot = top[i];

endif

top[i]++;

endfor

ITCAM[slot].valid = 0;

endif

```

Figure 21. Scheme 1 algorithm to free a slot previously occupied by a prefix of length len

Figure 22. ITCAM layout for Scheme 2

```

Algorithm: getSlot(len)

ma = movesFromAbove(len, &aPos);

mb = movesFromBelow(len, &bPos);

if (ma < mb)

d = getFromAbove(len, aPos);

if (top[len] > bot[len]) bot[len] = d;

top[len] = d;

else

if (mb == W) throw NoSpaceException;

d = getFromBelow(len, bPos);

if (top[len] > bot[len]) top[len] = d;

bot[len] = d;

endif

return d;

```

Figure 23. Scheme 2 algorithm to get a free slot to insert a prefix whose length is len

The scheme 3 *getSlot* algorithm (Figure 27) first attempts to make available a slot from the doubly-linked list for the desired block. When this list is empty, the algorithm behaves like the *getSlot* algorithm for Scheme 2 and the supporting algorithms of Figure 28 are similar to the corresponding supporting algorithms for Scheme 3.

The algorithm to free a slot (Figure 29) differs from that for Scheme 2 in that when the slot being freed is inside a block it is added to the doubly-linked list of free slots. Again, correctness and consistency are established easily. Although the worst-case performance of the Scheme 3 algorithms is the same as that of the algorithms for the first two schemes, we expect the Scheme 3 algorithms to have better performance on average.

### 3.4.4 Scheme 4

This is the CAO\_OPT scheme presented in [23]. Here, prefixes are arranged in chain order, with the free space pool in the middle of the ITCAM. Figures 30–32 give the necessary algorithms. The interfaces are different from those used by the first 3 schemes. The input to getSlot is p, which is the node in the trie where the prefix being inserted is stored. Each trie node stores wt,  $wt_ptr$ ,  $hcld_ptr$ , lchild, rchild, which are explained in [23]. In addition to these we use the following variables:

```

Algorithm: movesFromAbove(len, *pos) // returns number of moves needed to acquire free space from above the

block of length len

moves=0;

for (p=len; top[p] > bot[p]; p--); // find max p \le len such that block p is not empty

for (c=len+1; c \le W+1; c++) // find min c > len with space just below it

if (top[c] \le bot[c]) // not empty

if (bot[c]+1 < top[p]) *pos = p; return moves; endif

moves++;

p = c;

endif

return W;

Algorithm: movesFromBelow(len, *pos) // returns number of moves needed to acquire free space from below the

block of length len

moves=0;

for (p=len; top[p] > bot[p]; p++); // find min p >= len such that block p is not empty

for (c=len-1; c>=0; c--) // find min c>len with space just below it

if (top[c] \le bot[c]) // not empty

if (top[c]-1 > bot[p]) *pos = p; return moves; endif

moves++;

p = c;

endif

return W;

Algorithm: getFromAbove(len, pos) // get free space from above

d = top[pos]-1;

for (c=pos; c > len; c--)

if (top[c] \le bot[c])

d = bot[c];

move(bot[c]--, --top[c]);

endif

return d;

Algorithm: getFromBelow(len, pos) // get free space from below

d = bot[pos]+1;

for (c=pos; c< len; c++)

if (top[c] \leq bot[c])

d = top[c];

move(top[c]++, ++bot[c]);

endif

return d;

```

Figure 24. Supporting algorithms used by the algorithm of Figure 23

# Algorithm: freeSlot(d, len) if (top[len] == d) ITCAM[top[len]++].valid = 0; else if (bot[len] == d) ITCAM[bot[len]--].valid = 0; else move (bot[len], d); ITCAM[bot[len]--].valid = 0; endif

Figure 25. Scheme 2 algorithm to free a slot

Figure 26. ITCAM layout for Scheme 3, with moves for insert and delete. The curved arrows on the right show the forward links in the list of free spaces.

slot: address of ITCAM slot in which prefix is entered. If prefix has not yet been entered, then this variable is set to -1.

firstFree: first free space lastFree: last free space

shift[0:W/2]: temporary array of nodes

Also needed is an array of nodes, say nodeMap[0:N] for ITCAM[0:N] that contains the node address of each valid prefix in the ITCAM, so that they can be located in the trie.

### 4 Wide Dual TCAM-DUOW

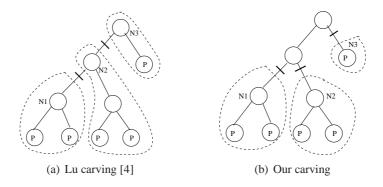

In this section we extend our DUOS scheme to the case when wide SRAMs (say, 144-bit words or larger) are in use. We describe the extension only for the case when the LSRAM is wide. The case when the ISRAM is wide uses techniques almost identical to those used in [4] while for a wide LSRAM, we need to modify these techniques. As in [4], a wide LSRAM word is used to store a subtree of the binary trie of a forwarding table. However, instead of beginning with the binary trie for all prefixes as is done in [4], we begin with the binary trie, leaf trie, for only the leaf prefixes. When a subtree of the leaf trie is stored in an LSRAM word, that subtree is removed from (or carved out of) the leaf trie before another subtree is identified for carving. Let N be the root of the subtree being carved and let Q(N) be the prefix defined by the path from the root of the trie to N. Q(N) is stored in the LTCAM, and  $|P_i| - |Q(N)|$  suffix bits, of each prefix  $P_i$  in the carved subtree rooted at N, are stored in the LSRAM word. Note that each suffix stored in the LSRAM word is a suffix of a leaf prefix that begins with Q(N). By repeating this carving process, all leaf prefixes are allocated to the LTCAM and LSRAM. To obtain the mapping of leaf prefixes to the LTCAM and LSRAM, we need a carving algorithm that ensures that the Q(N)s stored in the LTCAM are disjoint. Since the carving algorithm of [4] does not

```

Algorithm: getSlot(len)

aP=0; bP=0; aC=0; bC=0;

if (AV[len] == -1) // AV[len] stores the first free space in block of length len

ma = movesFromAbove(len, &aP, &aC);

mb = movesFromBelow(len, &bP, &bC);

if (ma < mb)

d = getFromAbove(len, aP, aC);

if (top[len] > bot[len]) bot[len] = d;

top[len] = d;

else

if (mb == W) throw NoSpaceException; // no space

d = \text{getFromBelow}(len, bP, bC);

if (top[len] > bot[len]) top[len] = d;

bot[len] = d;

endif

else

d = AV[len];

AV[len] = next[d];

endif

return d;

```

Figure 27. Scheme 3 algorithm to get a free slot to insert a prefix whose length is len

ensure disjointedness, a new carving algorithm is needed. As an example, consider the binary trie of Figure 33(a), which has been carved using a carving algorithm that ensures that each carved subtree has at most 2 leaf prefixes. The LTCAM will need to store Q(N1), Q(N2) and Q(N3). Even though the prefixes in the binary trie are disjoint, the Q(N) in the LTCAM are not disjoint (e.g., Q(N1)) is a descendant of Q(N2) and so Q(N2) matches all IP addresses matched by Q(N1)). To retain much of the simplicity of the LTCAM management scheme of DUOS it is necessary to carve the leaf trie in such a way that all Q(N)s in the LTCAM are disjoint.

As in [4], we carve via a postorder traversal of the binary trie. However, we use the visit algorithm of Figure 34 to do the carving. In this algorithm, w is the number of bits in an LSRAM word and  $x \rightarrow$  size is the number of bits needed to store (1) the suffix bits corresponding to prefixes in the subtrie rooted at x, (2) the length of each suffix, (3) the next hop for each suffix, (4) the number of suffixes in the word, and (5) the length of Q(x), which is the corresponding prefix stored in the LTCAM. Algorithm splitNode(q) (not specified in this paper) does the actual carving of the subtree rooted at node q. The basic idea in our carving algorithm is to forbid carving at two nodes that have an ancestor-descendent relationship. This ensures that the Q(N)s are disjoint. Figure 33(b) shows the subtrees carved by our algorithm. As can be seen, Q(N1), Q(N2), Q(N3) are disjoint. Although our carving algorithm generally results in more Q(N)s than when the carving algorithm of [4] is used, our carving algorithm allows us to retain the flexibility to store the Q(N)s in any order in the LTCAM as the Q(N)s are independent.

The LTCAM algorithms to insert, delete, change, and necessary support algorithms are given in Figures 35–39.

The function carve is invoked by both the insert and delete algorithms under different contexts that we analyze below. When a prefix is deleted, the LSRAM word storing its suffix (corresponding to the LTCAM word for Q(cNode)) may have remaining suffixes that can be merged with another LSRAM word. This merge is accomplished by the carve function, by carving the trie at tNode, which is the nearest ancestor with two children, of cNode. Thus carve helps to reduce the LTCAM entries by one. When a prefix is inserted, it may be possible to add the suffix bits of the new prefix in the LSRAM word that corresponds to the LTCAM slot for Q(cNode). If there is no cNode in the path between the new prefix node and the root, then we try to carve at tNode, which is the nearest degree 2 ancestor of the new prefix node, and therefore includes the new prefix along with other existing prefixes. So, in this case, using carve we prevent

```

Algorithm: movesFromAbove(len, *pos, *cur)

moves=0;

for (p=len; top[p] > bot[p]; p--); // find max p \le len such that block p is not empty

for (c=len+1; c\leq W+1; c++) // find min c>len with space just below it

if (top[c] \le bot[c]) // not empty

if (bot[c]+1 < top[p] || !valid[bot[c]])

*cur = c; *pos = p;

return moves;

endif

moves++;

if (AV[c] >= 0) *pos = c; *cur = c; return moves; endif

endif

return W;

Algorithm: movesFromBelow(len, *pos, *cur)

moves=0;

for (p=len; top[p] > bot[p]; p++); // find min p >= len such that block p is not empty

for (c=len-1; c>=0; c--) // find min c>len with space just below it

if (top[c] \le bot[c]) // not empty

if (top[c]-1 > bot[p] || !valid[top[c]])

*pos = p; *cur = c;

return moves;

endif

moves++;

if (AV[c] >= 0) *pos = c; *cur = c; return moves; endif

p = c;

endif

return W;

Algorithm: getFromAbove(len, p, c)

if (top[p] > bot[c]+1) d = top[p]-1; c = p;

else

if (!valid[bot[c]])

d = bot[c] - -;

if (d == AV[c]) AV[c] = next[AV[c]];

next[prev[d]] = next[d];

if (next[d] != -1) prev[next[d]] = prev[d];

endif

else

d = AV[c];

AV[c] = next[AV[c]];

move(bot[c], d);

d = bot[c] - -;

endif

c--;

endif

for (; c > len; c - -)

if (top[c] \leq bot[c])

20

move(bot[c]--, --top[c]);

d = bot[c]+1;

endif

return d;

```

```

Algorithm: freeSlot(d, len)

if (top[len] == d) ITCAM[top[len]++].valid = 0;

else if (bot[len] == d) ITCAM[bot[len]--].valid = 0;

else

ITCAM.invalidateWaitWrite(d, AV[len]); // AV[len] is stored in ISRAM[d].

if (AV[len]!=-1) prev[AV[len]] = d;

AV[len] = d;

endif

```

Figure 29. Scheme 3 algorithm to free a slot

```

Algorithm: getSlot(p)

d = isTopHeavy(p)? lastFree - -: firstFree + +;

if (parent(p) and p \rightarrow parent(p) \rightarrow slot < firstFree) // Case I: Insert prefix on top.

c = parent(p); i=0;

while (c and c \rightarrow slot < firstFree)

shift[i++] = c;

c = parent(c);

endwhile

for (j=i-1; j>=0; --j)

tmp = shift[j] \rightarrow slot;

move(shift[j] \rightarrow slot, d);

d = \text{tmp};

endfor

else if (\text{child}(p) \text{ and } \text{child}(p) \rightarrow slot > lastFree) // Case II: Insert prefix on bottom.

c = child(p); i=0;

while (c and c \rightarrow slot > lastFree)

shift[i++] = c;

c = child(p);

endwhile

for (j=i-1; j>=0; -j)

tmp = shift[j] \rightarrow slot;

move(shift[j] \rightarrow slot, d);

d = \text{tmp};

endfor

endif

return d;

```

Figure 30. Scheme 4 getSlot algorithm

```

Algorithm: freeSlot(d)

if (d < firstFree)

c = nodeMap[firstFree-1]; i=0;

while (c and c \rightarrow slot > d)

shift[i++] = c;

c = child(c);

endwhile

for (j=i-1; j>=0; -j)

tmp = shift[j] \rightarrow slot;

move(shift[j] \rightarrow slot, d);

d = \text{tmp};

endfor

firstFree - -;

else

c = nodeMap[lastFree+1]; i=0;

while (c and c \rightarrow slot < d)

shift[i++] = c;

c = parent(c);

endwhile

for (j=i-1; j>=0; -j)

tmp = shift[j] \rightarrow slot;

move(shift[j] \rightarrow slot, d);

d = \text{tmp};

endfor

lastFree ++;

endif

ITCAM[d].valid = 0;

```

Figure 31. Scheme 4 freeSlot algorithm

```

Algorithm: isTopHeavy(p)

top=bot=0;

for (c = parent(p); c != NULL; c = parent(c))

if (c \rightarrow slot > lastFree) bot++;

else top++;

for (c = p \rightarrow wt\_ptr; c != NULL; c = c \rightarrow wt\_ptr)

if (c stores a prefix)

if (c \rightarrow slot > -1) // prefix is already placed in TCAM

if (c \rightarrow slot > lastFree) bot++;

else top++;

else k++;

endif

endif

n = top+bot+k;

return (top > n/2) ? 1 : 0

Algorithm: parent(p)

c = p \rightarrow parentNode;

while (c and !c \rightarrow valid) c = c \rightarrow parentNode;

return c;

Algorithm: child(p)

c = NULL;

// don't return a LTCAM prefix as child.

if (p \rightarrow hcld\_ptr \text{ and } p \rightarrow hcld\_ptr \rightarrow tcam == 1) c = p \rightarrow hcld\_ptr;

return c;

```

Figure 32. Supporting control plane trie algorithms used by the Scheme 4 getSlot and freeSlot algorithms

Figure 33. Carving using the method of [4] and our method

```

Algorithm: visit_postorder(x)

if (!x) return 0;

isSplit = visit_postorder(y);

isSplit | = visit_postorder(z);

if (isSplit ||x→size > w) then

splitNode(y);

splitNode(z); // where y and z are children of x

return 1;

else if (x→size == w) then

splitNode(x);

return 1;

endif

return 0;

```

Figure 34. Algorithm to carve a leaf trie to obtain disjoint Q(N)s

```

Algorithm: insert(node, cNode, tNode)

// node: node in leaf trie for new prefix to be inserted.

// cNode: nearest carved ancestor in leaf trie of node (may be NULL).

// tNode: nearest degree 2 ancestor of node.

if (cNode)

d = cNode \rightarrow slot;

addSuffix(d, cNode, node);

LTCAM.invalidateWaitWrite(d, AV);

AV = d;

else if (!carve(tNode, node)) // create new suffix node with 1 sufix d = AV;

AV = next[d];

LTCAM.waitWriteValidate(d, Q(node), suffix);

node\rightarrowslot = d;

endif

```

Figure 35. DUOW algorithm to insert a prefix into the LTCAM

```

Algorithm: addSuffix(slot, cNode, node)

if (suffix does not fit in LSRAM[slot]) // need another suffix node

split(cNode);

cNode \rightarrow slot = -1;

else // add suffix to LSRAM[slot]

d = AV;

AV = next[d];

LTCAM.waitWriteValidate(d, LTCAM[slot], LSRAM[slot] + suffix);

cNode \rightarrow slot = d;

endif

```

Figure 36. Algorithm to add a suffix to a wide LSRAM word

```

Algorithm: split (cNode)

if (cNode \rightarrow y \text{ and } cNode \rightarrow z) // carve at children y & z of cNode

cNode \rightarrow y \rightarrow slot = AV;

cNode \rightarrow z \rightarrow slot = next[AV];

AV = next[next[AV]];

LTCAM.waitWriteValidate(cNode \rightarrow y \rightarrow slot, Q(cNode \rightarrow y), suffixes(cNode \rightarrow y));

LTCAM.waitWriteValidate(cNode \rightarrow z \rightarrow slot, Q(cNode \rightarrow z), suffixes(cNode \rightarrow z));

else if (cNode \rightarrow y) split (cNode \rightarrow y);

else split(cNode \rightarrow z);

endif

```

Figure 37. Algorithm to split a wide LSRAM word into two

```

Algorithm: delete(node, cNode, tNode)

// node: node in leaf trie corresponding to the prefix to be deleted

// cNode: nearest carved ancestor of node cannot be NULL

// tNode: nearest degree 2 ancestor node of cNode.

oldSlot = cNode \rightarrow slot;

p = number of suffixes in LSRAM[oldSlot];

if (p > 1 \text{ and } ! \text{carve}(tNode, cNode)) // delete suffix from its suffix node

d = AV;

AV = next[d];

LTCAM.waitWriteValidate(d, LTCAM[oldSlot], LSRAM[oldSlot] - suffix);

cNode \rightarrow slot = d;

else cNode \rightarrow slot = -1;

endif

LTCAM.invalidateWaitWrite(oldSlot, AV);

AV = oldSlot:

Algorithm: carve(tNode, cNode)

if (!tNode) return 0;

if (suffixes(tNode)) fit in a suffix node) // carve at tNode

d = AV;

AV = next[d];

LTCAM.waitWriteValidate(d, Q(tNode), suffixes(tNode));

tNode \rightarrow slot = d;

otherNode = the carvedNode in subtree rooted at tNode that is not cNode;

LTCAM.invalidateWaitWrite(otherNode\rightarrowslot, AV);

AV = otherNode \rightarrow slot;

otherNode\rightarrowslot = -1;

return 1;

endif

return 0;

```

Figure 38. DUOW algorithm to delete a leaf prefix

```

Algorithm: change(prefix, cNode, nexthop)

oldSlot = cNode\rightarrowslot;

d = AV;

AV = next[d];

newWord = LSRAM[oldSlot] with next hop for cNode \rightarrow prefix set to nexthop;

LTCAM.waitWriteValidate(d, prefix, newWord);

cNode \rightarrow slot = d;

LTCAM.invalidateWaitWrite(oldSlot, AV);

AV = oldSlot;

```

Figure 39. DUOW algorithm to change the next hop of a leaf prefix

the addition of a new LTCAM entry for the new prefix.

Next we show that tNode is indeed an appropriate node to carve and the algorithm preserves the property of carving at only one node along any path from the root. tNode is carved only if the number of bits needed to store all suffixes in the subtree rooted at tNode is less than the size of an LSRAM word. In this case there is a single otherNode that is a descendant of tNode and for which Q(otherNode) is in the LTCAM. To see that there cannot be more than one otherNode, suppose there are q such nodes with Q(q) in the LTCAM. All of these q nodes must be in the subtree of tNode that does not contain the target node, which is cNode for a delete and the new prefix node for an insert. This is because, if there was one carved node t among the t nodes in the subtree of tNode, for a delete, then t must occur either in the path between tNode and tNode, or as a descendant of tNode, given that tNode is the nearest ancestor of tNode with two children. In either case, t violates the property of a single carving along any path from the root. Similarly for an insert, if there were a carved node t in the same subtree that contained the newly added prefix, then t would have served as the tNode and we would not have started the tNode algorithm in the first place. Since all tNode nodes must appear in the same subtree rooted at either the left or right child of tNode, and the sum of their sizes is small enough to fit in an LSRAM word, our carving algorithm would have carved that child of tNode. Thus there is only one tNode. Since we delete tNode and tNode and tNode or ight after adding tNode not property of carving only once along any path is maintained.

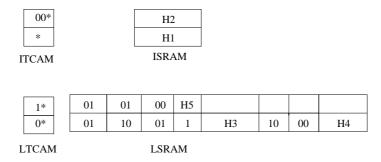

Figure 40 shows a possible assignment of the 5-prefix example in Figure 8. The intermediate prefixes P1 and P2 are stored in the ITCAM, while the leaf prefixes P3, P4 and P5 are stored in the LTCAM using a wide LSRAM. The suffix nodes begin with the prefix length field of 2 bits in this example followed by the suffix count field of 2 bits. Next comes the (length, suffix, nexthop) triplet for each prefix encoded in the suffix node, the number of allocated bits being (2bits, 4 bits, 6 bits) respectively for the three fields in the triplet.

Figure 40. Assignment of prefixes of Figure 8 to the two TCAMs in the dual TCAM architecture

### 5 Indexed DUOW-IDUOW

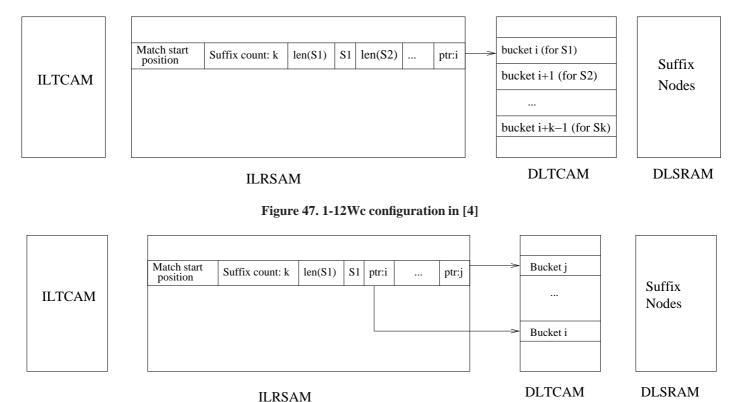

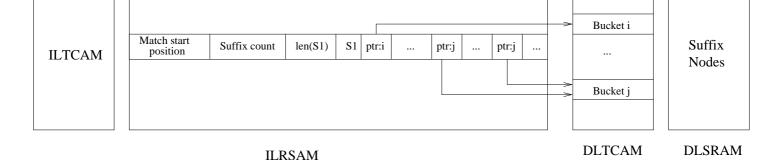

Zane et al. [21] introduced the concept of an indexed TCAM that reduces significantly the power consumed by a TCAM lookup. This concept was refined by Lu and Sahni [4] to reduce both the TCAM power and space requirements substantially. We show how to incorporate an index TCAM in conjunction with an LTCAM that uses a wide LSRAM (i.e., an index for the LTCAM of DUOW). Adding an index to the ITCAM of DUOW follows easily from [4]. When the LTCAM is indexed, we have two TCAMs replacing the LTCAM—a data TCAM referred to as DLTCAM and in index TCAM referred to as ILTCAM. The associated SRAMs are DLSRAM and ILSRAM.

We consider the two most effective index TCAM strategies of [4]–1-12Wc and M-12Wb. The former is best for power whereas the latter is the best overall scheme consuming least TCAM space and low power for lookups [4]. Both 1-12Wc and M-12Wb organize the DLTCAM into fixed size buckets that are indexed using the ILTCAM and ILSRAM, which also is a wide SRAM that stores suffixes and associated information.

### 5.1 Memory Management for DLTCAM and ILTCAM

Each DLTCAM bucket is assigned a unique number between 0 and totalSlots/bucketSize, where totalSlots is the total number of DLTCAM slots. The unique number so assigned to a bucket is called its index. A bucket index is stored in the trie node (in field bIndex) that is carved and represents an index prefix enclosing the DLTCAM prefixes in the bucket. The free slots in a bucket are linked through the associated DLSRAM. The first several bits (32 should be enough) of a DLSRAM word store the address of the next free DLTCAM slot in the same bucket. The last free slot in a bucket stores -1 in bits 0-31 of the corresponding DLSRAM word. For each bucket we keep one free slot at all times. This free slot is used for consistent updates, to copy the new prefix before deleting the old one. The first free slot in a bucket is stored in an array AV indexed by the bucket index. The array AV is initialized and maintained in the control plane. A list of free buckets is maintained in the DLSRAM using additional bits of each DLSRAM word (12 bits are sufficient when the number of buckets is at most 4096). The first available slot in a free bucket stores the bucket index of the next free bucket in the DLSRAM bits and so on. The free bucket chain is terminated by a -1 in the bits used to store the index of the next free bucket. The variable bucketAV keeps track of the first bucket on the free bucket chain. In our algorithms we use the array nextBucket to represent the forward links in the bucket list.

When the prefixes in an ILTCAM are disjoint, we may use the simple memory management scheme used for the LTCAM of DUOS and when these prefixes are not disjoint, they must be ordered and any of the memory management schemes proposed for the ITCAM of DUOS in Section 3.4 may be used.

The update algorithms (Figures 41–46) are almost identical for 1-12Wc and M-12Wb. We explain the differences in the next two subsections.

### 5.2 1-12Wc

This two-level TCAM organization in [4] employs wide SRAMs in association with both the data and index TCAMs as shown in the Figure 47. The strategy adopted in [4] to fill up the TCAMs and the SRAMs is summarized as follows. Firstly, suffix nodes are created for prefixes in the 1-bit trie, as described in Section 4, using Lu's carving heuristic. Secondly, every Q(N) to be entered in the data TCAM, is treated as a prefix and the subtree split algorithm [4] is applied to carve index nodes in the trie. The carving is done so that the number of data TCAM prefixes enclosed by the node being carved, is less than or equal to the size b of a data TCAM bucket. A new bucket is assigned to every index node. An enclosed data TCAM prefix and the corresponding suffix node are entered in a new entry in the bucket. When an index node encloses fewer than b prefixes, the remaining entries in the bucket are padded with null prefixes. Finally, the index nodes are treated as prefixes, the algorithm to create suffix nodes is run on the trie containing only index prefixes. The newly carved index Q(N) prefixes and the corresponding suffix nodes are entered in the index TCAM and the associated wide SRAM respectively. Using this strategy, the bucket numbers corresponding to the suffixes in an index SRAM suffix node, happen to be consecutive. Hence, the index SRAM omits the bucket number for all suffixes except the starting suffix, as shown in the Figure 47.

```

Algorithm: insert(node, cNode, tNode, isramNode, itcamNode, itNode)

// node: node in leaf trie for new prefix to be inserted.

// cNode: nearest carved ancestor in leaf trie of node (may be NULL).

//tNode: nearest degree 2 ancestor of node.

// isramNode: index node enclosing cNode

// itcamNode: node whose prefix exists in ILTCAM.

// itNode: nearest degree 2 ancestor of isramNode.

if (cNode)

bucketIndex = isramNode \rightarrow bIndex;

d = cNode \rightarrow slot;

addSuffix(d, cNode, node, isramNode, itcamNode, itNode);

DLTCAM.invalidateWaitWrite(d, AV[bucketIndex]);

AV[bucketIndex] = d;

else if (!carve(tNode, node, bucketIndex)) // create new suffix node with 1 sufix

if (isramNode) then

bucketIndex = isramNode \rightarrow bIndex;

d = AV[bucketAV];

AV[bucketAV] = next[d];

if (AV[bucketAV] == -1) then

splitBucket(isramNode, itcamNode, itNode);

if (node \rightarrow slot == -1) // slot has not been assigned in splitBucket

N = descendant of isramNode pointing to a DTCAM bucket and enclosing node.

newd = AV[N \rightarrow bIndex];

AV[N \rightarrow bIndex] = next[newd];

AV[bucketAV] = d;

d = newd;

endif

endif

if (node \rightarrow slot == -1)

DLTCAM.waitWriteValidate(d, Q(node), suffix);

decrementRoom(bucketIndex);

endif

else

assignNewBucket(node);

d = AV[node \rightarrow bIndex];

AV[node \rightarrow bIndex] = next[d];

DLTCAM.waitWriteValidate(d, Q(node), suffix);

node \rightarrow slot = d;

ILTCAM.insert(node, NULL, NULL);

endif

endif

```

Figure 41. DLTCAM insert algorithm

```

Algorithm: addSuffix(slot, cNode, node, isramNode, itcamNode, itNode)

if (suffix does not fit in DLSRAM[slot]) // need another suffix node

split(cNode, isramNode, itcamNode, itNode);

cNode→slot = -1;

else // add suffix to DLSRAM[slot]

bucketIndex = isramNode→bIndex;

d = AV[bucketIndex];

AV[bucketIndex] = next[d];

DLTCAM.waitWriteValidate(d, DLTCAM[slot], DLSRAM[slot] + suffix);

cNode→slot = d;

endif

```

Figure 42. Add a suffix to a DLSRAM word

During incremental updates, if a bucket overflows then assigning a new bucket immediately next to the overflowing bucket may require a large number of moves. Hence the suffix node format in IDUOW stores the bucket number for each suffix, which makes it possible to assign any empty bucket in case of an overflow. The suffix node format for the ILSRAM for 1-12Wc is shown in Figure 48. Also, in keeping with the main idea of storing independent prefixes in the LTCAM, the *visit\_postorder* algorithm is used instead of the subtree split algorithm in [4] while filling out the TCAMs. The prefix assignment algorithm for 1-12Wc is given below.

- 1. Suffix nodes corresponding to prefixes in the forwarding table are created using the *visit\_postorder* algorithm on the 1-bit leaf prefix trie as shown in Section 4.

- 2. Each Q(N) prefix resulting from Step 1 is to be entered into DLTCAM and is marked as a DLTCAM prefix in the trie.

- 3. The  $visit\_postorder$  algorithm is applied to carve the index prefix nodes. The symbols used in the  $visit\_postorder$  algorithm have slightly different meaning now:  $x \rightarrow size$  represents the number of DLTCAM prefixes enclosed by node x, and w is b-1, where b is the size of a DLTCAM bucket with one free slot for consistent updates. As an index node is carved, the enclosed DLTCAM prefixes are entered in a new DLTCAM bucket, and the bucket index is stored in the trie node, corresponding to the index, in field bIndex.

- 4. Each Q(N), for the index nodes carved in Step 3, is marked as an index prefix in the trie.

- 5. Suffix nodes are created for the index prefixes using the  $visit\_postorder$  algorithm on the 1-bit trie containing the index prefixes. The Q(N) prefixes corresponding to the carved nodes are entered in the ILTCAM. Suffixes for the index prefixes are entered in ILSRAM along with their bucket indexes, in the ILSRAM suffix node format as shown in the Figure 48.

The functions incrementRoom and decrementRoom are not relevant for 1-12Wc and are null functions. The assignNewBucket function is outlined in Figure 49.

The 1-12Wc scheme loses space efficiency as we carve out independent index prefix nodes and use a single bucket to store the DLTCAM prefixes enclosed by a single index prefix. The M-12Wb scheme doesn't have this deficiency as DLTCAM prefixes from index prefixes are stored in the same bucket.

### 5.3 M-12Wb

The characteristic of the many-1 schemes in [4] is that all DTCAM buckets, except the last one, can be completely filled. Thus multiple index nodes use the same bucket to store their enclosed data TCAM prefixes. The configuration for M-12Wb is shown in Figure 50. The algorithm for carving and prefix assignment follows:

```

Algorithm: split (cNode, isramNode, itcamNode, itNode)

if (cNode \rightarrow y \text{ and } cNode \rightarrow z) // carve at children y & z of cNode

bucketIndex = isramNode \rightarrow bIndex];

if (next[AV[bucketIndex]] == -1 || next[next[AV[bucketIndex]]] == -1)

splitBucket(isramNode, itcamNode, itNode); // AV[bucketIndex] should get reset here

if (isramNode is not the same as cNode) then

if (cNode \rightarrow y \rightarrow slot == -1) then

N = descendant of isramNode pointing to a DTCAM bucket and enclosing node.

cNode \rightarrow y \rightarrow slot = AV[N \rightarrow bIndex];

cNode \rightarrow z \rightarrow slot = next[AV[N \rightarrow bIndex]];

AV[N \rightarrow bIndex] = next[next[AV[N \rightarrow bIndex]]];

decrementRoom(N \rightarrow bIndex, 2);

endif

incrementRoom(bucketIndex, 1);

if (cNode \rightarrow y \rightarrow slot == -1)

cNode \rightarrow y \rightarrow slot = AV[isramNode \rightarrow child[0] \rightarrow bIndex];

AV[isramNode \rightarrow child[0] \rightarrow bIndex] = next[cNode \rightarrow y \rightarrow slot];

decrementRoom(isramNode \rightarrow child[0] \rightarrow bIndex, 1);

endif

if (cNode \rightarrow z \rightarrow slot == -1)

cNode \rightarrow z \rightarrow slot = AV[isramNode \rightarrow child[1] \rightarrow bIndex];

AV[isramNode \rightarrow child[1] \rightarrow bIndex] = next[cNode \rightarrow z \rightarrow slot];

decrementRoom(isramNode \rightarrow child[1] \rightarrow bIndex, 1);

incrementRoom(bucketIndex, 1);

endif

else

cNode \rightarrow y \rightarrow slot = AV[bucketIndex];

cNode \rightarrow z \rightarrow slot = next[AV[bucketIndex]];

AV[bucketIndex] = next[next[AV[bucketIndex]]];

decrementRoom(bucketIndex, 1);

endif

DLTCAM.waitWriteValidate(cNode\rightarrowy\rightarrowslot, Q(cNode\rightarrowy), suffixes(cNode\rightarrowy));

DLTCAM.waitWriteValidate(cNode \rightarrow z \rightarrow slot, Q(cNode \rightarrow z), suffixes(cNode \rightarrow z));

else if (cNode \rightarrow y) split (cNode \rightarrow y);

else split(cNode \rightarrow z);

endif

```

Figure 43. Split a DLSRAM word

```

Algorithm: delete(node, cNode, tNode, isramNode, itcamNode, itNode)

// node: node in leaf trie corresponding to the prefix to be deleted

// cNode: nearest carved ancestor of node, cannot be NULL

//tNode: nearest degree 2 ancestor node of cNode.

// isramNode: index node enclosing cNode

// itcamNode: node whose prefix exists in ILTCAM.

//itNode: nearest degree 2 ancestor of itcamNode.

bucketIndex = isramNode \rightarrow bIndex;

oldSlot = cNode \rightarrow slot;

p = number of suffixes in DLSRAM[oldSlot];

if (p > 1 and !carve(tNode, cNode, bucketIndex)) // delete suffix from its suffix node

d = AV[bucketIndex];

AV[bucketIndex] = next[d];

DLSRAM[d] = DLSRAM[oldSlot] - suffix;

DLTCAM[d].prefix = DLTCAM[oldSlot].prefix;

DLTCAM[d].valid = 1;

cNode \rightarrow slot = d;

else

cNode \rightarrow slot = -1;

if (isramNode \rightarrow size == 0) then // bucket becomes empty

deleteBucket(isramNode, itcamNode, itNode);

endif

decrementRoom(bucketIndex);

endif

DLTCAM.invalidateWaitWrite(oldSlot, AV[bucketIndex]);

AV[bucketIndex] = oldSlot;

Algorithm: carve(tNode, cNode, bucketIndex)

if (!tNode) return 0;

if (suffixes(tNode) fit in a suffix node) // carve at tNode

d = AV:

AV = next[d];

DLSRAM[d] = suffixes(tNode);

DLTCAM[d].prefix = Q(tNode);

DLTCAM[d].valid = 1;

tNode \rightarrow slot = d;

otherNode = the carvedNode in subtree rooted at tNode that is not cNode;

DLTCAM.invalidateWaitWrite(otherNode\rightarrowslot, AV[bucketIndex]);

AV[bucketIndex] = otherNode \rightarrow slot;

otherNode\rightarrowslot = -1;

return 1;

endif

return 0;

```

Figure 44. Delete a leaf prefix

```

Algorithm: change(prefix, cNode, nexthop, isramNode)

oldSlot = cNode \rightarrow slot;

bucketIndex = isramNode \rightarrow bIndex;

d = AV[bucketIndex];

AV[bucketIndex] = next[d];

newWord = DLSRAM[oldSlot] with next hop for cNode \rightarrow prefix set to nexthop;

DLTCAM.waitWriteValidate(d, prefix, newWord);

cNode \rightarrow slot = d;

DLTCAM.invalidateWaitWrite(oldSlot, AV[bucketIndex]);

AV[bucketIndex] = oldSlot;

Algorithm: deleteBucket(isramNode, itcamNode, itNode)

bucketIndex = isramNode \rightarrow bIndex;

nextBucket[bucketIndex] = bucketAV;

bucketAV = bucketIndex;

isramNode \rightarrow bIndex = -1;

ILTCAM.delete(isramNode, itcamNode, itNode);

Algorithm: splitBucket (isramNode, itcamNode, itNode)

if (isramNode \rightarrow y \text{ and } isramNode \rightarrow z) // carve at children y & z of isramNode

// We want to move the split child that contains fewer prefixes.

if (isramNode \rightarrow y \text{ contains fewer prefixes})

isramNode \rightarrow y \rightarrow bIndex = isramNode \rightarrow bIndex;

assignNewBucket(isramNode \rightarrow z);

node = isramNode \rightarrow z;

else

assignNewBucket(isramNode \rightarrow y);

isramNode \rightarrow z \rightarrow bIndex = isramNode \rightarrow bIndex;

node = isramNode \rightarrow y;

ILTCAM.insert(isramNode \rightarrow y, itcamNode, itNode);

ILTCAM.insert(isramNode \rightarrow z, itcamNode, itNode);

ILTCAM.delete(isramNode, itcamNode, itNode);

deletePrefixes(node);

else if (isramNode \rightarrow y) splitBucket(isramNode \rightarrow y, itcamNode, itNode);

else splitBucket(isramNode \rightarrow z, itcamNode, itNode);

endif

```

Figure 45. Change the next hop of a leaf prefix

### **Algorithm:** deletePrefixes(node)

```

bucketIndex = node \rightarrow bIndex;

len = length of deleteList;

for (i=0; i<len; ++i)

slot = deleteList[i];

DLTCAM.invalidateWaitWrite(slot, AV[bucketIndex]);

AV[bucketIndex] = slot;

incrementRoom(bucketIndex);

endfor

clear deleteList;</pre>

```

Figure 46. Delete prefixes

Figure 48. Our 1-12Wc configuration

### 1. Step 1: [Seed the DLTCAM buckets]

Run  $feasible ST2(T, b-1) \lceil n/(b-1) \rceil$  times. // b-1, since one free slot is needed in a bucket for consistent updates.

Each time call splitNode to carve the found bestST from T (thereby updating T) and pack bestST into a new DLTCAM bucket.

The function splitNode adds one or more prefixes to the ILTCAM.

### 2. Step 2: [Fill the buckets]

While there is a DLTCAM bucket that is not full and T is not empty, repeat Step 3.

## **Algorithm:** assignNewBucket(node)

node \rightarrow bIndex = bucketAV;

if (bucketAV == -1) throw NoBucketsException;

bucketAV = nextBucket[bucketAV];

Figure 49. Assign a new bucket in 1-12Wc

Figure 50. M-12Wb configuration in [4]

### 3. Step 3: [Add to a bucket]

Let B be the DLTCAM bucket with the fewest number of prefixes.

Let s be the number of prefixes in B.

Run feasible ST2(T, b - s).

Using splitNode carve the found bestST from T (thereby updating T) and pack bestST into B.

The function splitNode adds one or more prefixes to the ILTCAM.

# 4. Step 4: [Use additional buckets as needed]

While T is not empty, fill a new DLTCAM bucket by making repeated invocations of feasible ST2(T,q), where q is the remaining capacity of the bucket.

Add ILTCAM prefixes as needed.

There are three main differences between this algorithm and the PS2 algorithm in [4]. The first difference is reflected in the visit2 algorithm (invoked by feasibleST2) in that covering prefixes are not stored in the TCAMs. The second difference is in supplying b-1 as available space in an empty bucket of size b, reserving one free slot for consistent updates. The third difference is in the use of carving function splitNode which helps to create independent prefixes for IDUOW.

Apart from the data structures already defined for the two-level indexing schemes, the M-12Wb requires a doubly linked list of used buckets to keep track of the buckets and the available spaces in them. An instance of a class BList is maintained in the control plane which contains the doubly linked list of buckets as well as an array to get to the right bucket quickly using a bucket index. Each bucket in the list has fields room to indicate available bucket slots and index to indicate the index of the bucket. The room in a bucket decreases from head to tail of the list. BList uses function add to add a new bucket to the list and the array and getBucket to get the appropriate bucket based on bucket index.

### **6 Experimental Results**

We evaluated the performance of the different versions of DUO using 21 IPv4 routing tables and update sequences downloaded from [6] and [7]. Figure 55 gives the characteristics of these datasets. The update sequences for the first 20

# Algorithm: visit2(x) d = count(x); // returns the number of DLTCAM prefixes. $if (d \leq q \text{ and } d > bestCount)$ bestST = ST(x); bestCount = d; endif // check T - ST(x) d = count(root(T)) - count(x); $if (d \leq q \text{ and } d > bestCount)$ bestST = T - ST(x); bestCount = d; endif

Figure 51. Visit algorithm

```

Algorithm: splitNode(N, NoN)

NoN is trie node x if bestST = T-ST(x), otherwise NoN is passed as NULL. if (!N \mid | N == NoN) return; if (N \rightarrow \text{istouched} == 0)

N \rightarrow \text{istouched} = 1;

N \rightarrow \text{bIndex} = \text{BList.} head \rightarrow \text{index}; fill bucket with DLTCAM prefixes in N. Let s = \text{number of DLTCAM prefixes in } N. BList.head \rightarrow \text{room} = \text{BList.} head \rightarrow \text{room} - s. endif splitNode(N \rightarrow y); splitNode(N \rightarrow z);

```

Figure 52. Split a node

```

Algorithm: assignNewBucket(node)

Let s = \text{number of DLTCAM prefixes in } node.

if (s < BList.head \rightarrow room)

node \rightarrow bIndex = BList.head \rightarrow index;

BList.head \rightarrow room = s;

else if (bucketAV > -1)

node \rightarrow bIndex = \text{bucketAV};

BList.add(\text{bucketSize, bucketAV});

BList.head \rightarrow room = s;

bucketAV = nextBucket[bucketAV];

else

if (BList.head \rightarrow room == 1) throw NoSpaceException;

Run step 3 in PS2 while node still has a prefix;

endif

```

Figure 53. Assign a new bucket

### Algorithm: incrementRoom(bucketIndex)

b = BList.getBucket(bucketIndex);

$b \rightarrow room++;$

if  $b \rightarrow prev$  and  $b \rightarrow room > b \rightarrow prev \rightarrow room$  then relocate b to restore order.

### Algorithm: decrementRoom(bucketIndex)

b = getBucket(bucketIndex);

$b \rightarrow room$ -;

if  $b \rightarrow next$  and  $b \rightarrow room < b \rightarrow next \rightarrow room$  then relocate b to restore order.

Figure 54. Increment and decrement room

routing tables were captured from files storing update announcements from 12am on February 1, 2009 for the stated number of hours; the update sequence for the last routing table rc00May20 was captured from files storing eight hours of activity starting from 12am on May 20, 2008. The columns labeled #RawInserts, #RawDeletes and #RawChanges,

| DataSet          | #Prefixes | Collection Period (hours) | #RawInserts | #RawDeletes | #RawChanges |

|------------------|-----------|---------------------------|-------------|-------------|-------------|

| rrc00            | 294098    | 75.7                      | 39553       | 40051       | 368013      |