|

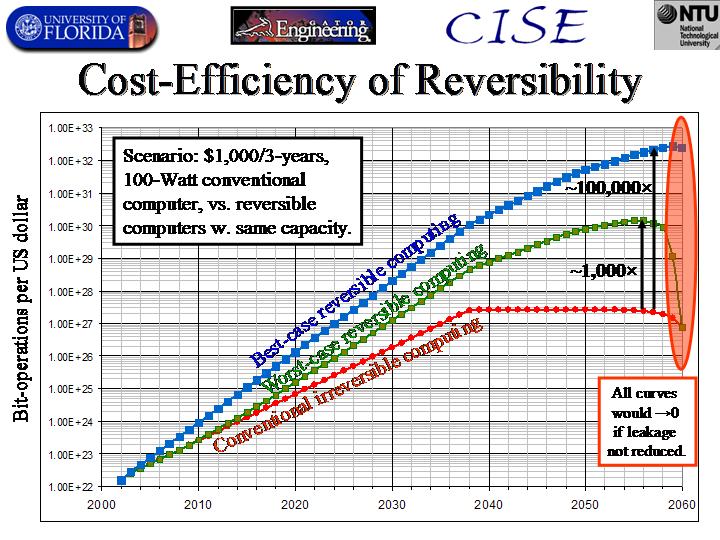

| Results from a detailed numerical model of cost-efficiency of reversible versus irreversible computers in future generations of technology. The cost-efficiency of irreversible computing eventually hits a thermodynamic brick wall, and cannot improve further as long as the cost of energy (and/or the heat flux limit of the cooling technology) is fixed. In contrast, the cost-efficiency of reversible computing can continue to improve far beyond this point, limited only by achievable energy leakage rates, which have no known fundamental lower limit. (However, for generating this graph, an arbitrary lower limit of 1 kT/ms/bit-device was assumed.) Note that the advantages of reversible computing could rise to 1,000-100,000x by the 2050s. This model even takes into account the algorithmic overheads of reversibility and the proportionality of energy dissipation to speed in adiabatic processes. These results were first published in Michael P. Frank, "Nanocomputer Systems Engineering" (.doc,.ps), 2003 Nanotechnology Conference & Trade Show, Feb. 23-27, 2003, San Francisco, CA. |